## Garrett's Workshop REU Clone

By Zane Kaminski

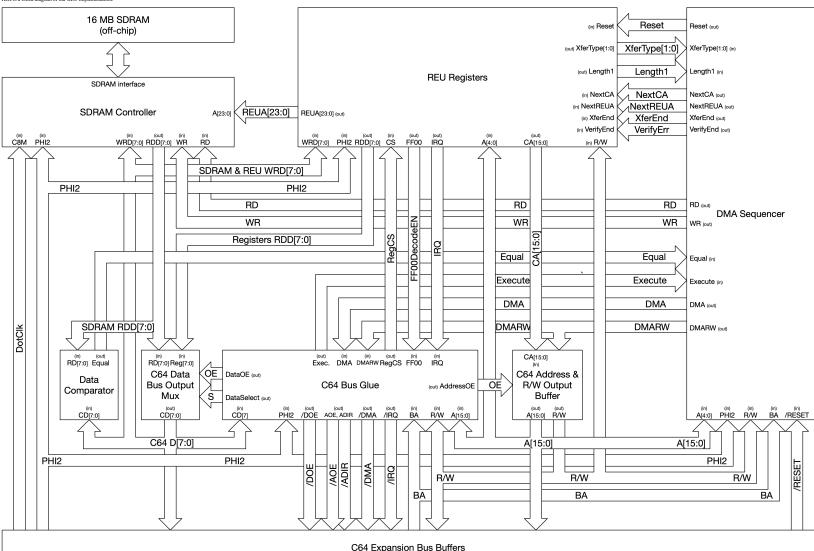

are we have chosen to implement the REU. All of this but for the SDRAM chip and level-shifting buffers will be implemented in a small CPLD or FPGA. We have divided the design into six main subsystems. These are

#### 1. SDRAM controller and its associated SDRAM

- SDFANG Control et all to associated SDFANG

SCRU registers

A EXE or register

Stage that an comparator (used for verify operation) and data output mux (chooses between register and DMA data)

Address output buffer

O DMA sequencer

## Here is a block diagram of our REU implementation:

We are going to go over each subsystem and describe its functionality.

### 1. SDRAM Controller

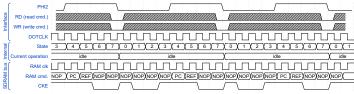

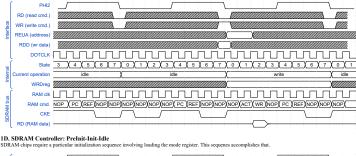

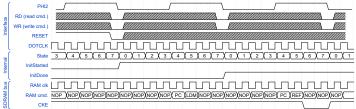

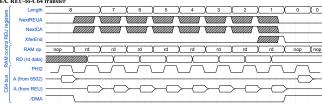

1. DEPARTMENT CONTINUED: First Will go over the SDRAM doubsystem. The SDRAM controller is the simplest part of the system since its interface is so straightforward and there are not many REU-specific details in the SDRAM controller except for the timing of the access sequence. We wanted to get the complexity of SDRAM out of the rest of the system so that there we could focus semantics. The SDRAM controller is clocked by the 8 MHz CG4 dotclock and the the SDRAM iself is clocked by the inversion of the dotdlock. This clocking arrangement makes for plenty of hold time at the SDRAM and half a clock less access latency than if the controller and there as the main of the controller and there are not many REU-specific details in the SDRAM and half a clock less access latency than if the controller and wret clocked by the PHI2 clock in the PHI2 clock in the PHI2 clock in the the PHI2 clock in the system so that the 6502 bus. Addresses are excepted by the controller at the first dot clock where PHI2 is low. This allows commands to commands to commands to calc the PHI2 clock in the first bed by the PHI2 click in the 6502 bus. Addresses are directly fed to the SDRAM controller register block. SDRAM access is conducted during PHI2 bus period and is completed just as PHI2 goes high again. During PHI2 high the SDRAM is refreshed rediately begin er

# 1A. SDRAM Controller: Idle-Idle-Idle

ation and when no SDRAM requests are p of the SDRAM of ing timing diagran

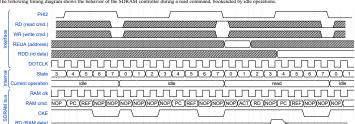

1C. SDRAM Controller: Idle-Write-Idle The following timing diagram shows the behavior of the SDRAM controller during a write command, bookended by idle of the source of the state of the source of the state of the source of

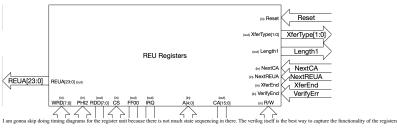

## 2. REU Registers

The REU registers block encapsulates the register functionality of the REU while exposing the minimum interface to the rest of the system. The register block integrates the interrupt, autoload, address increment, and length decrement functionality. The block has a single read/write port to service accesses from the 6502. The registers are read asyr synchronously at the falling edge of PHI2. The register block also outputs the REU address REUA[25:0] to the SDRAM as well as the C64 address CA[15:0] back to the Commodore. The length register, however, is not output from the register block. Instead the Length I signal indicates to the DMA Sequencer when the length register is equal to 1

Increment, decrement, and interrupt control is provided to the REU registers block by the DMA sequencer via the NextCA, NextREUA, XferEnd, and VerifyErr signals. When the NextREUA signal is high at the falling edge of PHI2, the KEUA address is incremented. Similarly, when NextCA is high at the falling edge of PHI2, the KEUA address is incremented. Similarly, the NextCA is high at the falling edge of PHI2, the KEUA address is incremented. The 6502 interrupt and autoload functionality. When XferEnd and VerifyErr signals are used to invoke the interrupt and autoload functionality to the invoke dif these features are enabled in the relevant registers. Similarly the VerifyErr signal, when asserted concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, the relevant register. This causes the autoload and interrupt functionality to be set in the register set. Similarly the VerifyErr signal, when asserted concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd at the falling edge of PHI2, concurrent with XferEnd a

## 3, 4, 5. Data Path, Address Output Buffer, 6502 Bus Glue

We let's get the small blocks out of the way before discussing the DMA sequencer. The function of the address output buffer block is just to output the CA address during DMA cycles. The data comparator is an asynchronous equality comparator which reports to the DMA sequencer whether the value read from SDRAM is the same as the value on the C64 data bus. The data output mux selects data from the register block or the SDRAM controller to be output to the C64 data bus based on whether DMA is occurring. On to the 6502 bus glue. Simple as it sounds, this piece is just asynchronous decode-type logic that selects the register block, controls the bus buffers, etc.

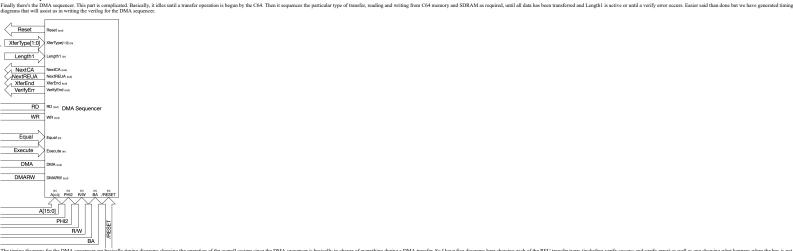

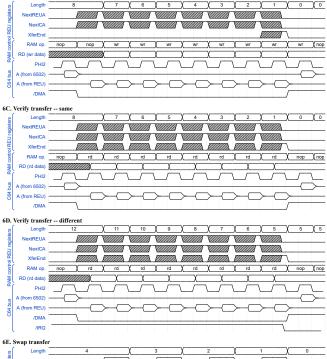

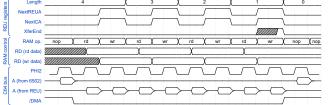

## 6. DMA Sequencer

The timing diagrams for the DMA sequencer are basically timing diagrams showing the operation of the overall system since the DMA sequencer is basically in darge of everything during a DMA transfer. So I have five diagrams here showing each of the REU transfer types (including verify success and verify error) as well as one showing what happens when the bus is not valiable. When the bus is not valiable, the DMA sequencer is the part of the CML and the DMA sequences in the the DMA sequences is a transfer types (including verify success and verify error) as well as one showing what happens when the bus is not valiable. The the bus is not valiable, the DMA sequencer is the part of the CML and the transfer types (including verify success and verify error) as well as one showing the device of the transfer types (including verify success and verify error) as well as one showing what happens when the bus is not valiable. The the bus is not valiable, the DMA sequencer is the part of the transfer types (including verify success and verify error) as well as one showing that happens when the bus is not valiable.

6A. REU-to-C64 transfer

6B. C64 to REU transfer

### 6F. Bus not available during DMA transfer to REU

| 01.1                            | Dus not avana | able uul li | ig Data th                                   | insici to p | ullo -   |          |         |                                              |           |         |         |         |          |

|---------------------------------|---------------|-------------|----------------------------------------------|-------------|----------|----------|---------|----------------------------------------------|-----------|---------|---------|---------|----------|

| ٤                               | Length        |             | 8                                            | χ 7         | χ 6      | 5        | χ 4     | χ 4                                          | χз        | χ 2     | χ 1     | X 0     | <u>)</u> |

| C64 bus RAM control REU registe | NextREUA      | _           | <i>\        </i>                             | VIIIIIIA    | VIIIIIIA | VIIIIIIA | VIIIIIA | VIIIIIIA                                     | VIIIIIIA  |         | VIIIIIA |         |          |

|                                 | NextCA        |             | <i>\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\</i> |             | V/////// |          |         | <i>\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\</i> |           |         |         |         |          |

|                                 | XferEnd       |             |                                              |             |          |          |         |                                              |           |         |         | \       |          |

|                                 | RAM op.       | nop         | (пор                                         | χ wr        | χ wr     | χ wr     | χ wr    | ) wr                                         | χ wr      | χ wr    | ) wr    | wr      | (nop     |

|                                 | RD (wr data)  |             |                                              | 8           | χ        | χ        | χ       | χ                                            | χ         | χ       | χ       | χ       |          |

|                                 | PHI2          |             | $\sim$                                       | $\Box$      | $\Box$   | $\Box$   | $\Box$  | $\Box$                                       | $\square$ | $\Box$  |         |         | <b>`</b> |

|                                 | A (from 6502) | C           | $\rightarrow$                                |             |          |          |         |                                              |           |         |         | —-C     | $\sim$   |

|                                 | A (from REU)  |             | C                                            | $\succ$     | $\succ$  | $\succ$  | $\succ$ | C_                                           | $\succ$   | $\succ$ | $\succ$ | $\succ$ |          |

|                                 | /DMA          |             | <b>`</b>                                     |             |          |          |         |                                              |           |         |         | /       |          |

|                                 | ВА            |             |                                              |             |          |          | ∖       |                                              |           |         |         |         | <u> </u> |

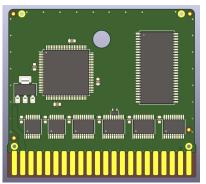

Layout Study We have prepared a quick layout study confirming that we can fit a TQFP-100 CPLD or FPGA, SDRAM, voltage regulator, and level-shifting buffers in the PCB size for a "stumpy" size cartridge. I think we have to add USB self-update functionality through so that will make it a bit tighter than this current layout concept