# SERVICE MANUAL MODEL C64 COMPUTER SEPTEMBER 1985 PN-314001-02

**Commodore Business Machines, Inc.** 1200 Wilson Drive, West Chester, Pennsylvania 19380 U.S.A.

> Commodore makes no expressed or implied warranties with regard to the information contained herein. The information is made available solely on an as is basis, and the entire risk as to quality and accuracy is with the user. Commodore shall not be liable for any consequential or incidental damages in connection with the use of the information contained herein. The listing of any available replacement part herein does not constitute in any case a recommendation, warranty or guaranty as to quality or suitability of such replacement part. Reproduction or use without expressed permission, of editorial or pictorial content, in any matter is prohibited.

This manual contains copyrighted and proprietary information. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission of Commodore Electronics Limited.

Copyright  $\textcircled{\mbox{\scriptsize C}}$  1985 by Commodore Electronics Limited. All rights reserved.

# CONTENTS

()

| Title                                  | Page  |

|----------------------------------------|-------|

| SPECIFICATIONS                         | 1     |

| PRODUCT PARTS LIST                     | 2     |

| BLOCK DIAGRAM                          | 3     |

| CIRCUIT THEORY                         |       |

| POWER SUPPLY                           | 4     |

| RESET LOGIC                            | 5     |

| CLOCK CIRCUITS                         | 6     |

| I/O, ROM, EXPANSION PORT               | 7     |

| RAM CONTROL LOGIC                      | 8     |

| 5 PIN VIDEO AND AUDIO OUTPUTS          | 9     |

| 8 PIN VIDEO AND AUDIO OUTPUTS          | 10    |

| CASSETTE INTERFACE                     | 11    |

| KEYBOARD, JOYSTICK & PADDLE INTERFACES | 12    |

| SERIAL INTERFACE, USER PORT            | 13    |

| TROUBLESHOOTING GUIDE                  | 14    |

| BOARD IDENTIFICATION                   | 17    |

| PCB ASSEMBLY #326298-01                |       |

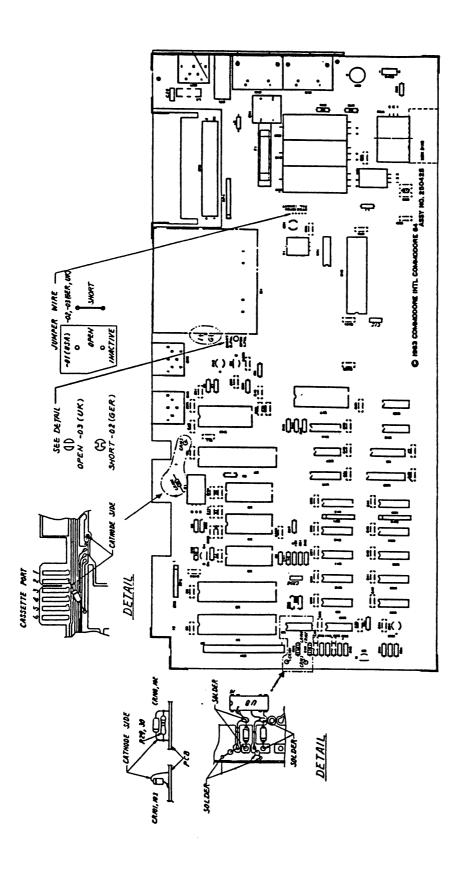

| BOARD LAYOUT                           | 18    |

| PARTS LISTS                            | 19,20 |

| PIN ASSIGNMENTS                        | 21    |

| SCHEMATIC #326106                      | 21,22 |

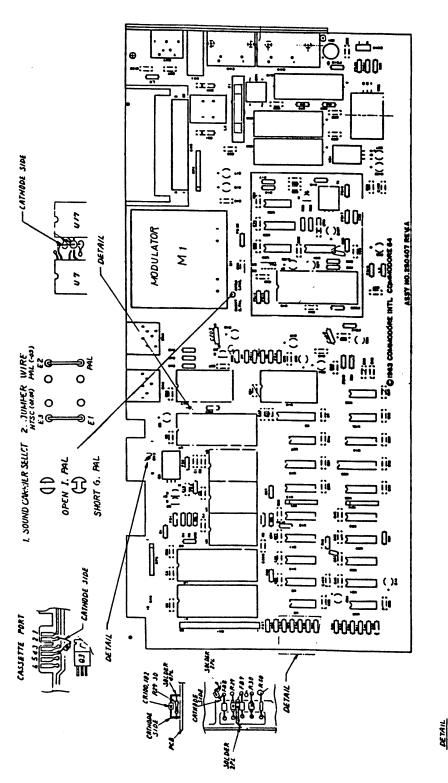

| PCB ASSEMBLY #250407-04                |       |

| BOARD LAYOUT                           | 23    |

| PARTS LIST                             | 24,25 |

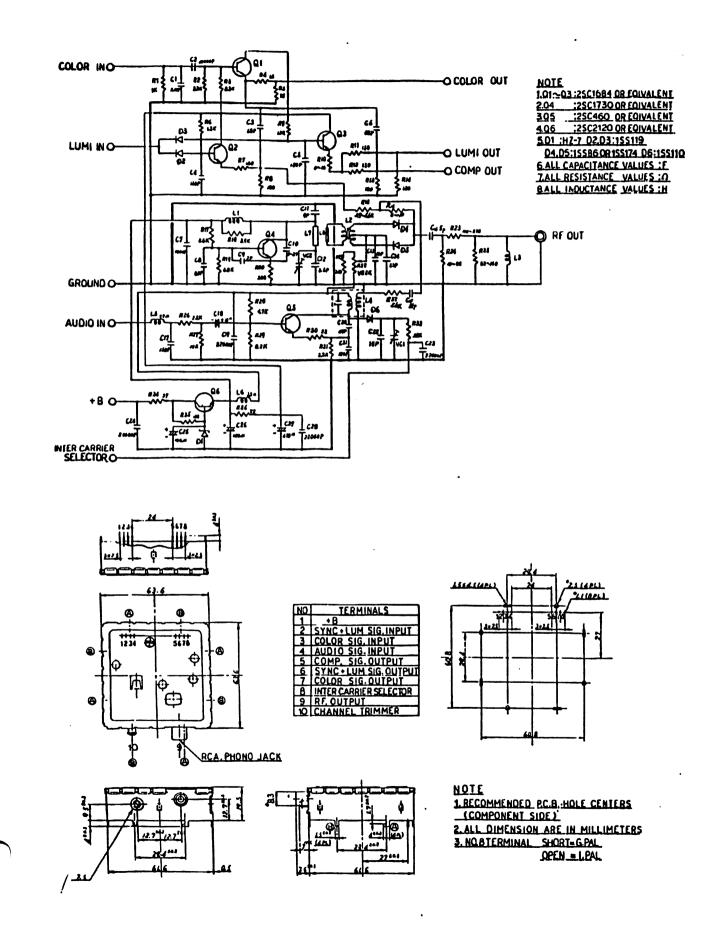

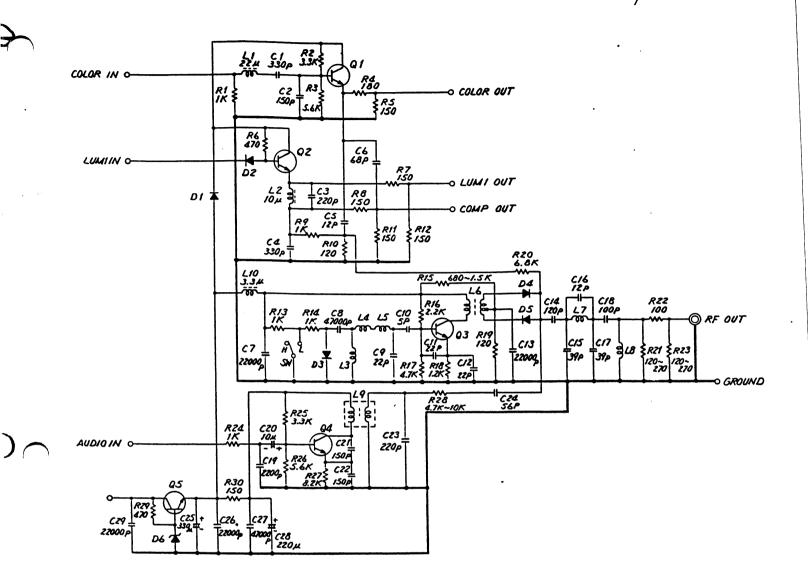

| MODULATOR SCHEMATIC #251025            | 26    |

| SCHEMATIC #251138                      | 26,27 |

| PIN ASSIGNMENTS                        | 27    |

| PCB ASSEMBLY #250425-01                |       |

| BOARD LAYOUT                           | 28    |

| PARTS LIST                             | 29,30 |

| MODULATOR SCHEMATIC #251696            | 31    |

| SCHEMATIC #251469                      | 31,32 |

| PIN ASSIGNMENTS                        | 32    |

5

$( \frown$

5

C64 | COMPUTER

| GENERAL DESCRIPTION | • The "All Purpose" Commodore 64 is the complete computer for education, home or small business applications. Supported by quality peripherals and a full range of software, the Commodore 64 is perfect for the family. No other computer can offer such variety of uses and applications at such an affordable price.                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMORY              | • 64K RAM                                                                                                                                                                                                                                                                                                                                                                                                        |

| ROM                 | <ul> <li>20K ROM Standard (includes operating system and BASIC interpreter)</li> </ul>                                                                                                                                                                                                                                                                                                                           |

| MICROPROCESSOR      | 6510A Microprocessor—1.02 MHz clock     Compatible with     the 6502                                                                                                                                                                                                                                                                                                                                             |

| DISPLAY             | 40 Columns X 25 lines of text                                                                                                                                                                                                                                                                                                                                                                                    |

| COLORS              | <ul> <li>16 Background, border and character colors</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |

| CHARACTERS          | <ul> <li>Upper &amp; lower case letters, numerals and symbols</li> <li>Reverse characters</li> <li>All PET graphic characters</li> </ul>                                                                                                                                                                                                                                                                         |

| DISPLAY MODES       | <ul> <li>Text characters</li> <li>High resolution graphics</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| RESOLUTION          | • 320 X 200 Pixels                                                                                                                                                                                                                                                                                                                                                                                               |

| SPRITES             | <ul> <li>8 independent sprites</li> <li>Each consists of 24 X 21 pixels and<br/>up to 4 colors</li> <li>Each independently expandable horizontally<br/>and vertically</li> <li>Collision detection for sprite to sprite and data<br/>to sprite collisions</li> </ul>                                                                                                                                             |

| SOUND               | <ul> <li>6581 Sound Interface Device includes 3 independent tone<br/>generators—each with 9 octaves</li> <li>Each voice includes<br/>programmable ADSR generator (Attack, Decay, Sustain, Release)<br/>and control of sawtooth, triangle, square, variable pulse and noise<br/>waveforms</li> <li>Full filtering capabilities with low, high and band<br/>pass filters</li> <li>External sound, input</li> </ul> |

| KEYBOARD            | Full size typewriter style design                                                                                                                                                                                                                                                                                                                                                                                |

| KEYS                | <ul> <li>66 Keys total</li> <li>2 Cursor control keys</li> <li>4 Function keys (up to 8 user defined/programmable functions possible)</li> <li>Upper and lower case character set</li> <li>Graphic character set</li> </ul>                                                                                                                                                                                      |

| INPUTS/OUTPUTS      | User port     Serial port     ROM cartridge port     Joystick/ paddle port     Video port     C1530 Cassette drive interface port                                                                                                                                                                                                                                                                                |

| FEATURES            | <ul> <li>Built-in BASIC 2.0—over 70 commands, statements and<br/>functions</li> <li>Full screen editor</li> </ul>                                                                                                                                                                                                                                                                                                |

| PERIPHERALS         | C1541 Disk drive     C1530 Datasette     MPS 801 Dot matrix<br>printer     MPS 802 Dot matrix printer     MPS 803 Dot matrix<br>printer     DPS 1101 Daisey wheel printer     C1520<br>Plotter/Printer     C1702 Color monitor     CM141 Color monitor                                                                                                                                                           |

| POWER REQUIREMENTS  | • 120 Volts, 60 Hz                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | Specifications subject to change without notice.                                                                                                                                                                                                                                                                                                                                                                 |

:

# PARTS LIST C-64

PLEASE NOTE: Commodore part numbers are provided for reference only and do not indicate the availability of parts from Commodore. Industry standard parts (Resistors, Capacitors, Connectors) should be secured locally. Approved cross-references for TTL chips, Transistors, etc. will be available in manual form through the Service Department in November of 1984. Unique or non-standard parts will be stocked by Commodore and are indicated on the parts list by a "C".

### **TOP CASE ASSY**

| Top Case        | C 326113-01  |

|-----------------|--------------|

| Keyboard        | C 326166-02  |

| LED Plate       | C 326160-01  |

| Nameplate       | C 326161-01  |

| Lamp Holder Set | C 903820-03  |

| LED Assembly    | C 1001039-01 |

### **BOTTOM CASE ASSY**

| Bottom Case          | C 326114-01 |

|----------------------|-------------|

| Foot, Self-Adhesive  | Ć 950157-04 |

| PCB Shield Plate     | C 326131-01 |

| PCB Insulation Sheet | C 326288-01 |

#### ACCESSORIES

| Users Manual | C 320974    |

|--------------|-------------|

| Power Supply | C 251053-02 |

| RF Cable     | C 326189-01 |

| Switch Box   | C 904778-01 |

|              |             |

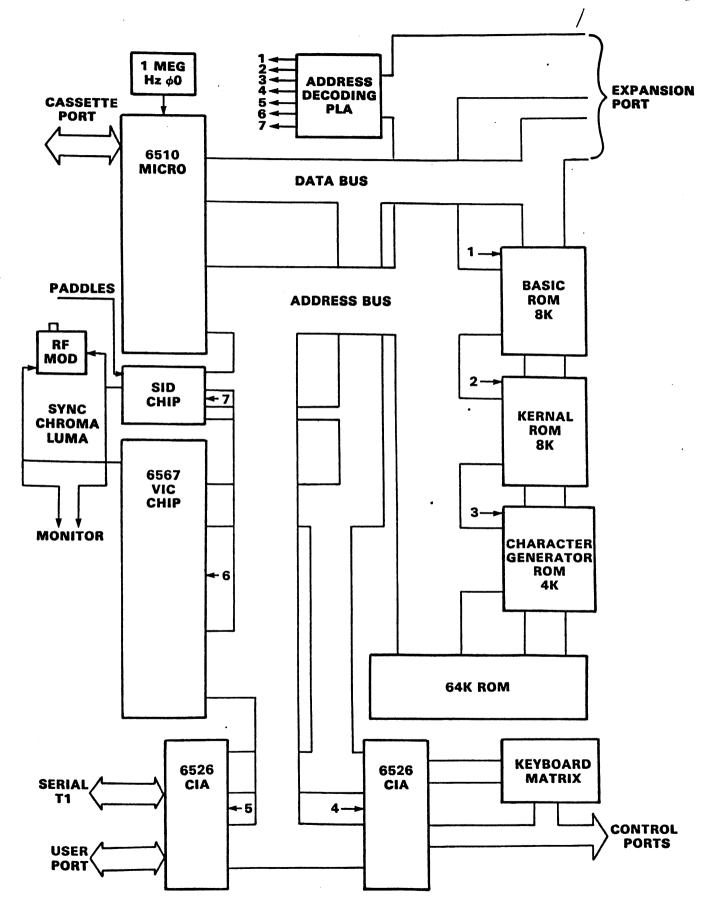

**C-64 BLOCK DIAGRAM**

5

(

•

:

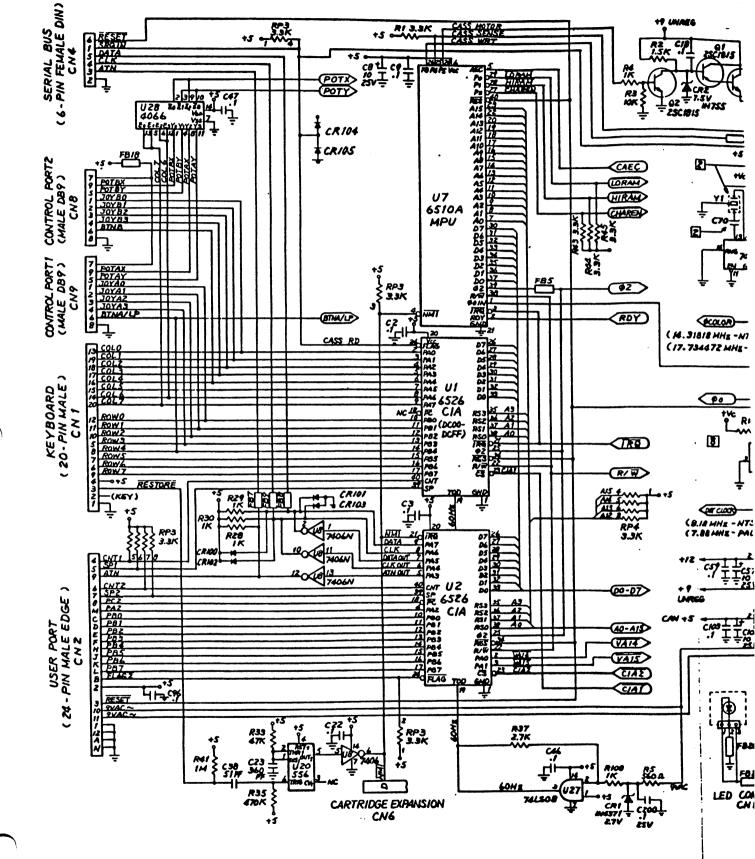

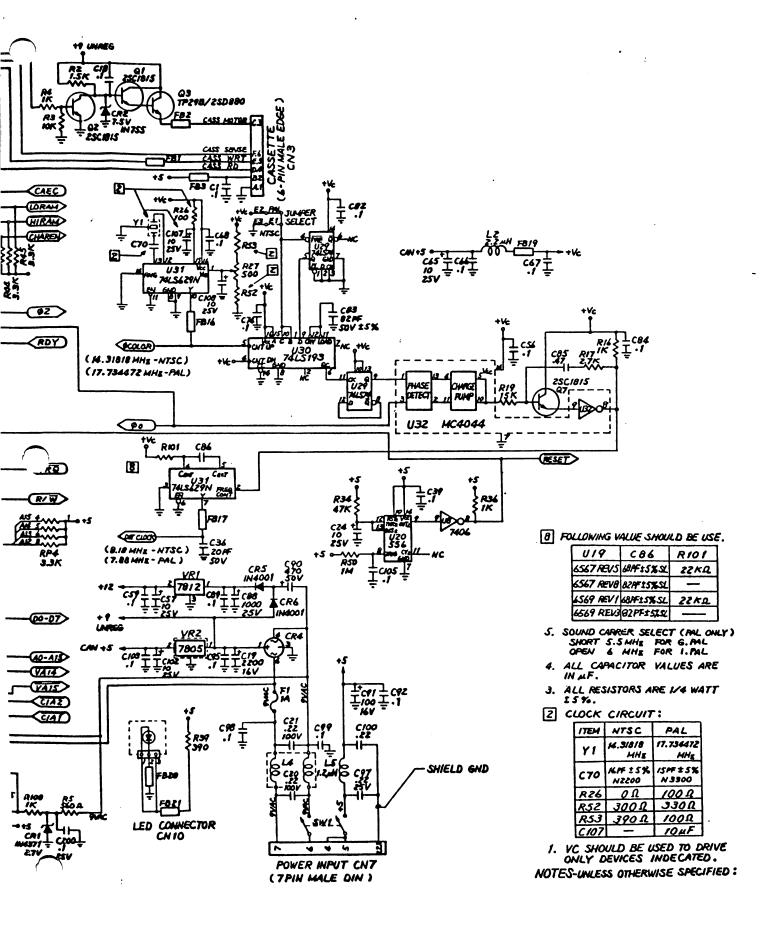

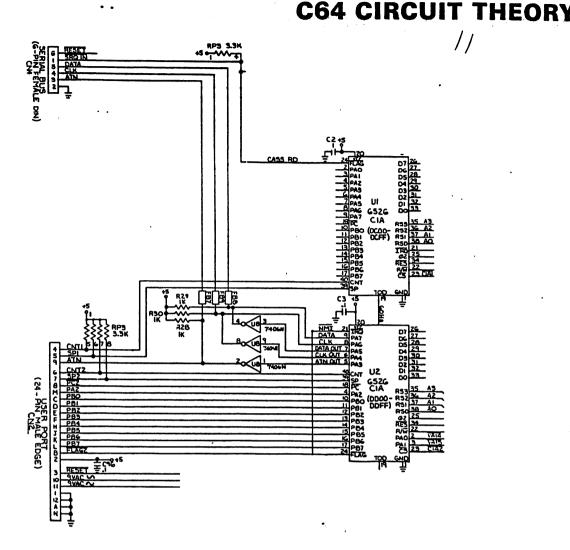

There are three versions of the C64. The C64 with a five pin connector video output (326106), The C64 with an eight pin connector video output (251138), and the C64B which has improved system clock circuit design (251469). Most circuit theory explanations will be the same for all three versions. Refer to schematic 326106 unless noted otherwise.

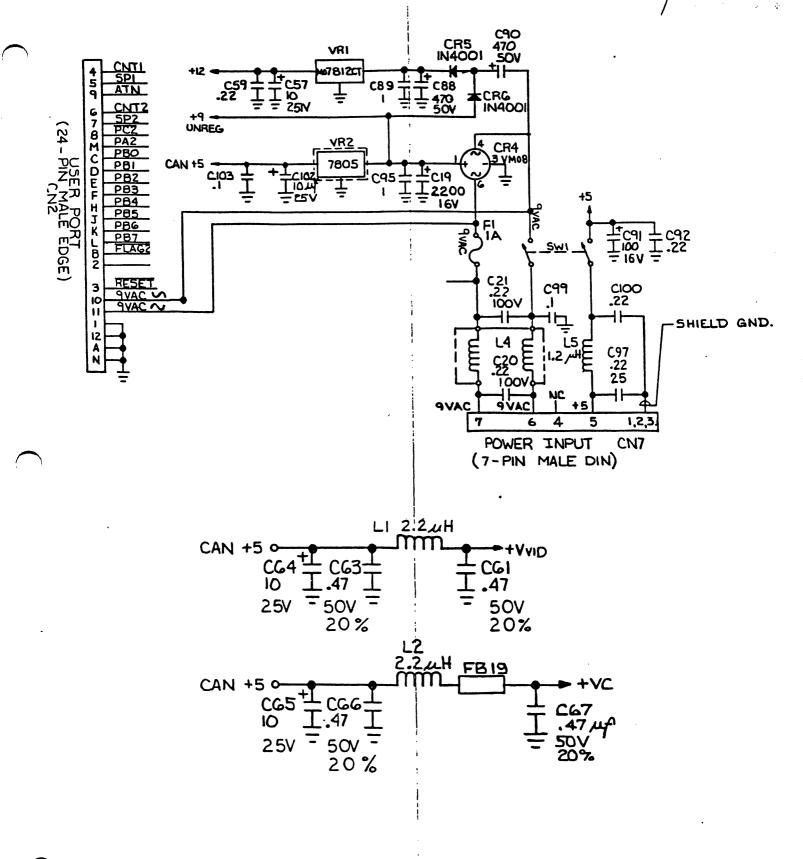

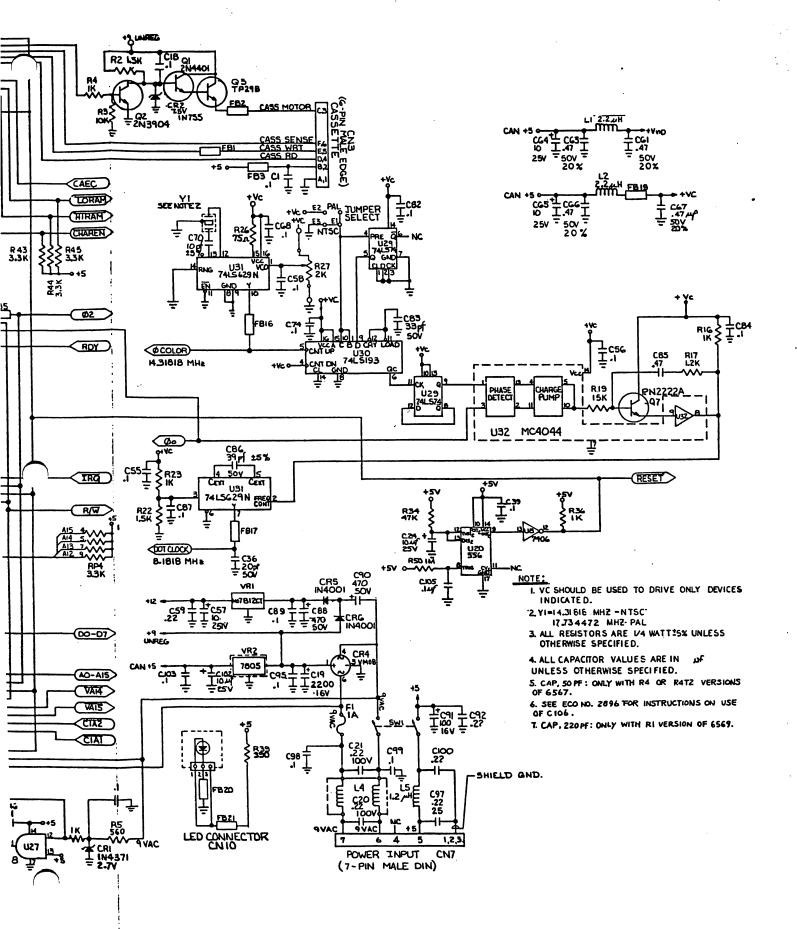

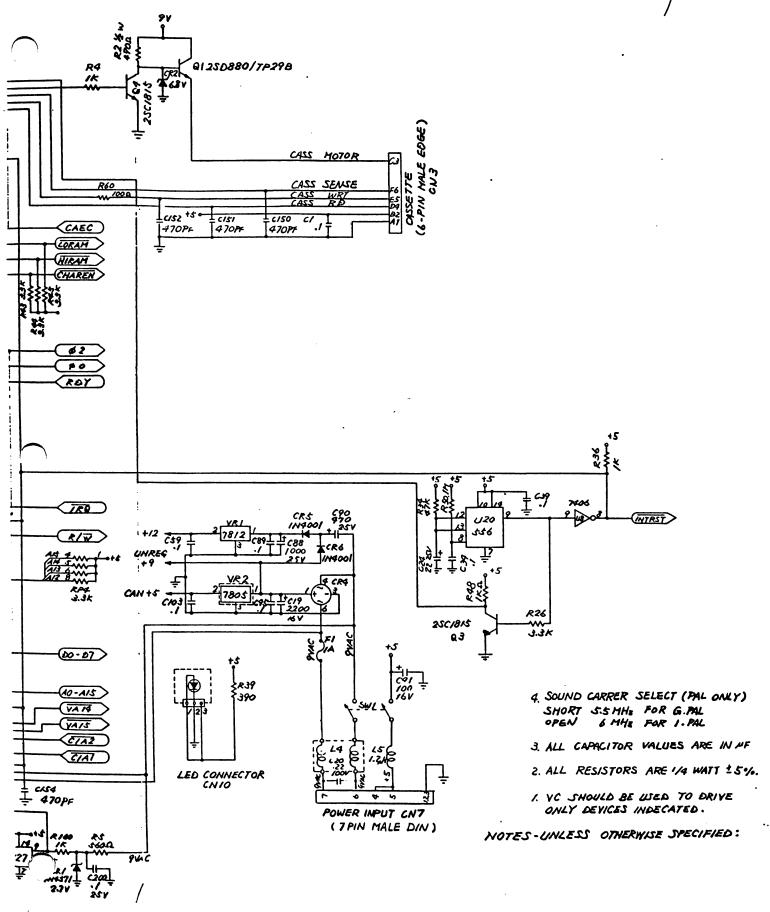

### The Power Supply.

The external power supply generates a regulated 5VDC and 9VAC. 5VDC is applied to pins 5 and 1 of CN7 on the C64 pcb. Filtered by L5,C97, and C100 it is then controlled by on/off switch S1. This 5VDC output supplies the microprocessor logic.

9VAC is applied to pins 6 and 7 of CN7 on the C64 pcb. +12VDC, +5VDC CAN and 9VDC unregulated are outputs that are derived from this 9VAC supply. The 9VAC supply is made available on pins 10 and 11 of the USER PORT CN2.

### **12VDC** Generation

9VAC is added to 9VDC through CR6, and rectified by CR5. The unregulated DC output is filtered by C88 and C89 then regulated at 12VDC by VR1. The regulated output is filtered by C57 and C59. The 12VDC supplies the VIC and SID IC, and the audio amplifiers.

#### +5VDC CAN Generation

9VAC is rectified by CR4. The unregulated DC output is filtered by C19, and C95 then regulated at 5VDC by VR2. The regulated output is filtered by C102 and C103. The output called 5VDC CAN is separated and individually filtered into two outputs called Vvid and Vc. Vvid is the 5VDC supply for the video circuits, and Vc is the 5VDC supply for the clock circuits.

### **9VDC Unregulated Generation.**

CR4 rectifies the 9VAC input. The output is 9VDC unregulated. This supply powers the cassette motor transistor amplifier circuits, and the RF modulator on the C64B version.

.

//

5

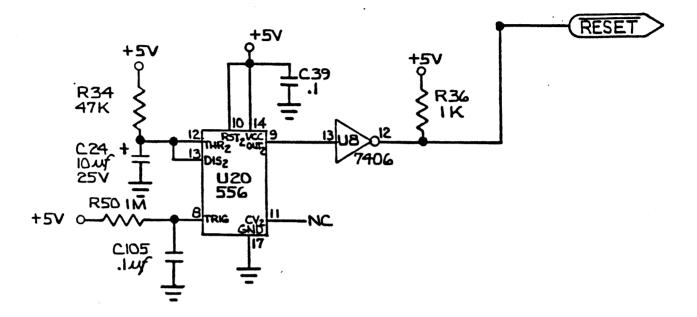

#### **Reset Logic Circuits.**

U20 is a 556 IC timer configured as a one shot multivibrator. The output pulse width is determined by the size of R34 and C24. Pulse width =  $1.1 \times R34 \times C24 \approx .5$  seconds. The output on pin 9 is "high" active. The output of U8 is "low" active. Reset initializes all the processor logic and causes the processor to load the program counter register with the address of the first instruction of the operating system program called the KERNAL. The starting address is stored in locations \$FFFC and \$FFFD. The first instruction is decoded and executed giving KERNAL control of the computer operations. The reset pulse occurs when turning the power on to the computer.

....

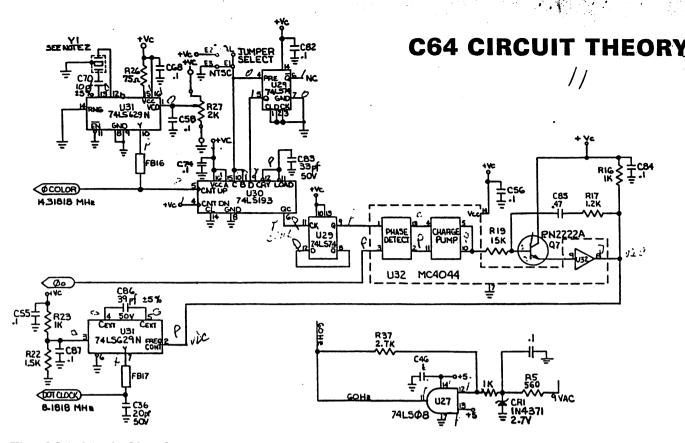

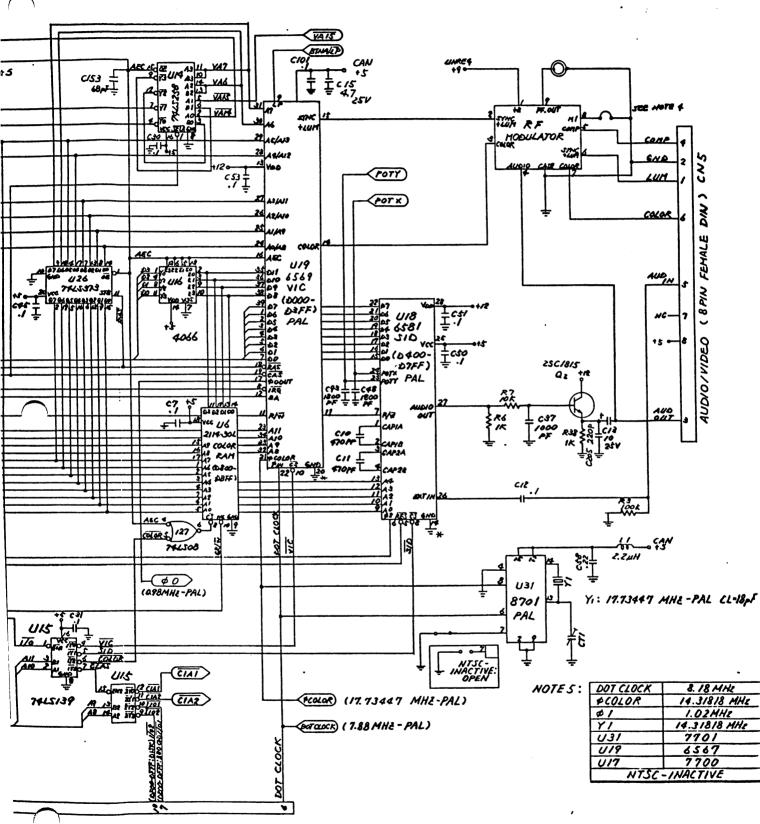

#### The C64 Clock Circuits.

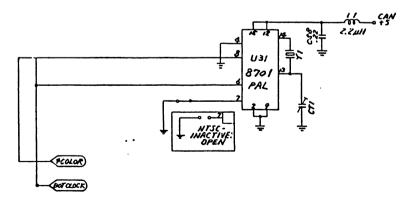

Crystal Y1 develops a 14.31818MHz fundamental frequency clock signal. U31 is a Dual Voltage Controlled Oscillator. The output on pin 10 is a 14.31818 MHz clock signal called the color clock. R27 can be adjusted to obtain exact output frequency. U30 is a frequency divider that outputs a 2MHz signal on pin 6. U29 is a D flip flop which outputs a 1MHz signal on pin 9. U32 is a Phase/Frequency Detector which compares the output of the U29 to the phase 0 clock, and outputs a dc voltage on pin 8 that is proportional to the phase difference between the inputs. The second half of the Dual Voltage Controlled Oscillator U31 generates an 8.1818MHz clock signal called the DOT Clock. The VIC IC divides the DOT clock by eight and outputs this as the phase 0 clock on pin 17. The output of the Phase/Frequency Detector is applied to the frequency control input pin 2 of U31. This causes tracking of the dot clock and the color clock because one input, pin 3 of U32, is the phase 0 clock which is derived from the dot clock, and the other input pin 1 of U32, is derived from the color clock.

### The C64B Clock Circuits. Refer to schematic 251469

Crystal Y1 develops the fundamental 16MHz clock signal. U31 is a Clock Generator IC that outputs the 8.1818MHz DOT clock on pin 6, and the 14.31818 MHz color clock on pin 8.

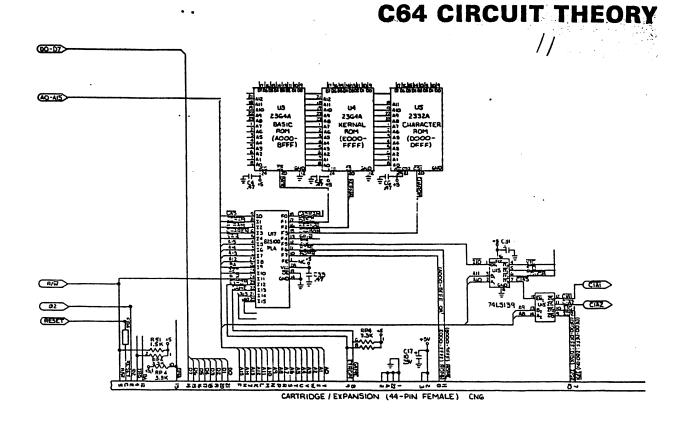

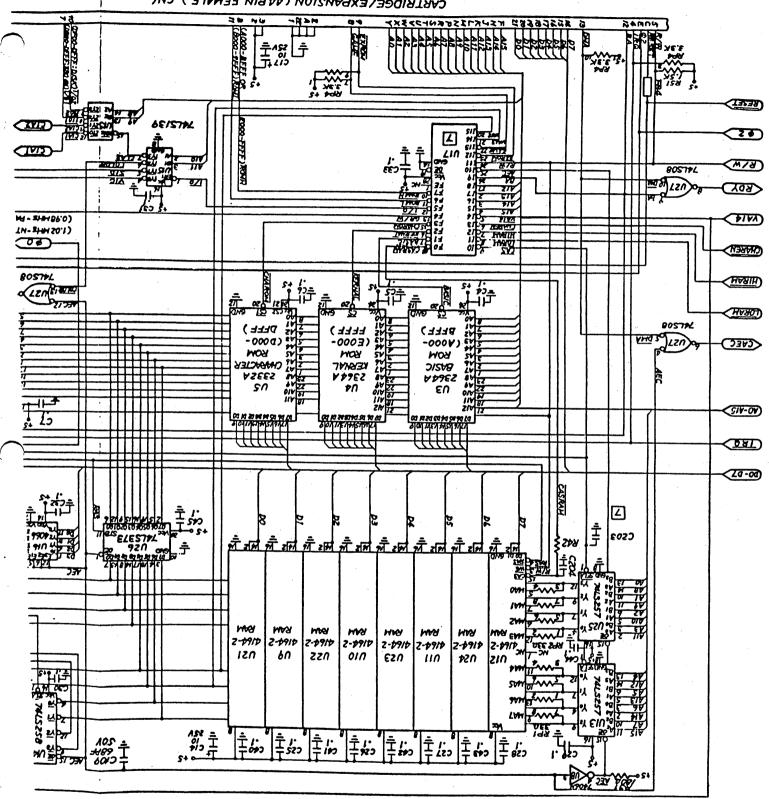

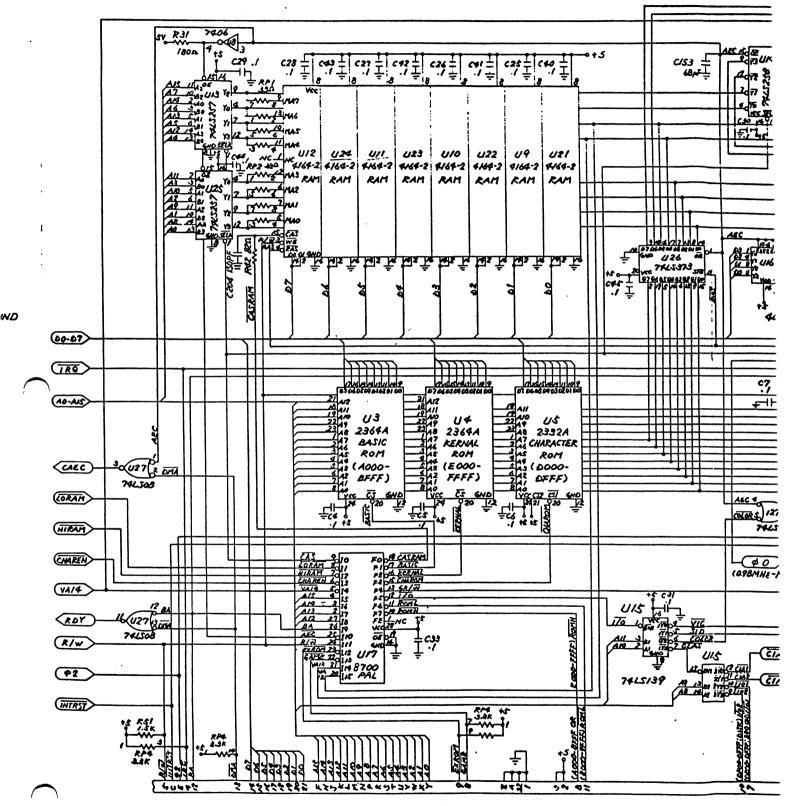

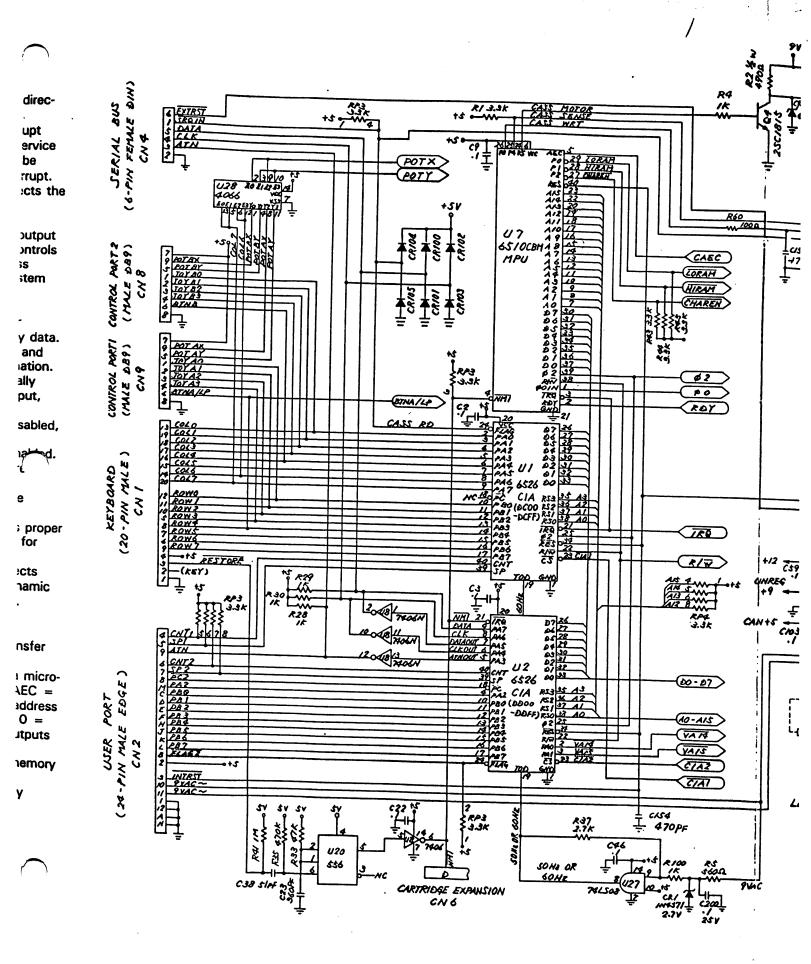

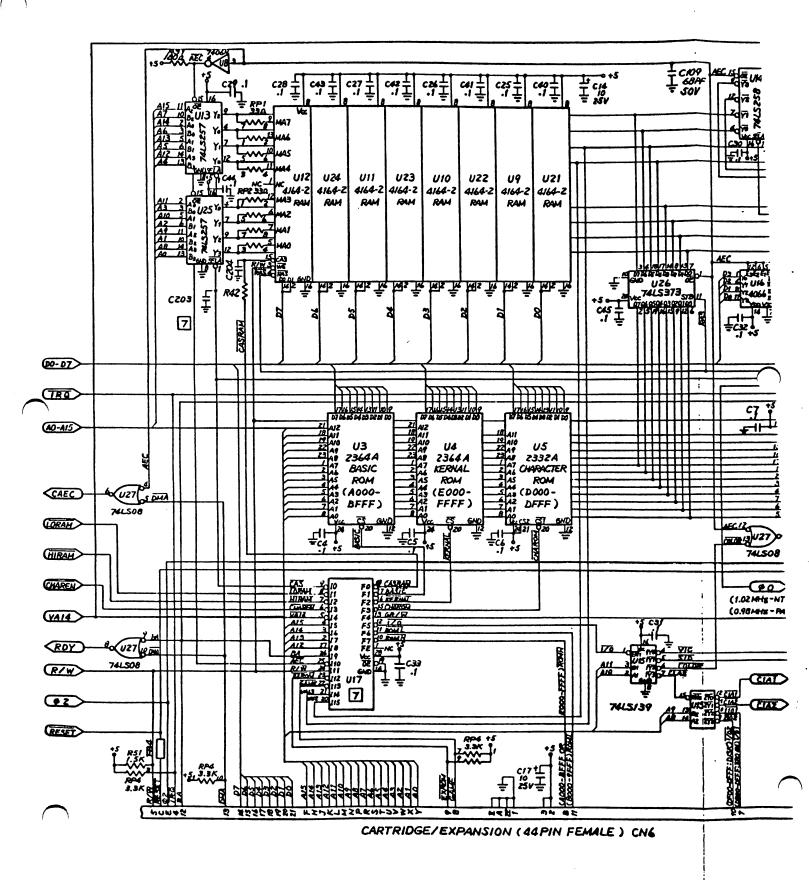

### I/O and ROM Address Decoding and Expansion Port.

### I/O Address Decoding Logic.

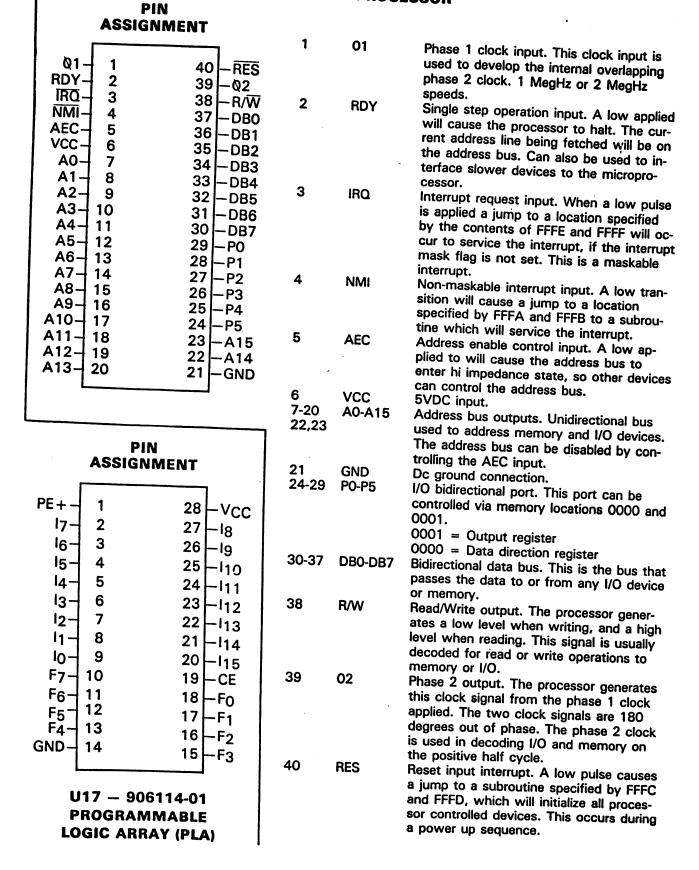

U17 is a Programmable logic array (PLA). The output F5 on pin 12 called I/O goes "low" when any of the I/O devices controlled by U15 are selected. The addresses are listed below for each device.

| VIC IC                | \$D000 - \$D02E                                       |

|-----------------------|-------------------------------------------------------|

| SID IC                | \$D400 - \$D7FF                                       |

| Color Ram             | \$D800 - \$DBFF                                       |

| CIA1                  | \$DC00 - \$DC0F                                       |

| CIA2                  | \$DD00 - \$DD0F                                       |

| I/O 1                 | \$DEOO - \$DEFF                                       |

| 1/0 2                 | \$DF00 - \$DFFF                                       |

| CIA1<br>CIA2<br>I/O 1 | \$DC00 - \$DC0F<br>\$DD00 - \$DD0F<br>\$DE00 - \$DEFF |

### **ROM Address Decoding.**

Basic ROM resides at locations \$A000 - \$BFFF. The output F1 pin 17 of the PLA U17 goes "low" when the BASIC ROM is selected. The KERNAL ROM resides at locations \$E000 - \$FFFF. The output F2 pin 16 of the PLA U17 goes "low" when the KERNAL ROM is selected. The CHARACTER GENERATOR ROM resides at locations \$D000 - \$DFFF. The output F3 pin 15 of the PLA U17 goes "low" when the Character Generator ROM is selected.

### The Expansion Port Connections.

The expansion port is an extension of the microprocessor address, data, and control bus. ROML decodes addresses \$8000 - \$9FFF, and ROMH decodes addresses \$E000 - \$FFFF. These are outputs from the PLA used to select the cartridge inserted in the expansion port. I/O 1 input from U15 decodes addresses \$DE00 - \$DEFF. I/O 2 output from U15 decodes addresses \$DF00 - \$DEFF.

|   |                                                   |                                                                                                                       | 6                                           | U7                 | 906107<br>Roproc | -01 /                                                                                                                                                                                                                                                                                                  |

|---|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 |                                                   | PIN                                                                                                                   |                                             |                    |                  | -2350K                                                                                                                                                                                                                                                                                                 |

|   |                                                   | ASSIGNMENT                                                                                                            |                                             |                    | _                |                                                                                                                                                                                                                                                                                                        |

|   | &1 -<br>RDY -<br>IRQ -<br>NMI -<br>AEC -<br>VCC - | 1 4<br>2 3<br>3 3<br>4 3<br>5 3                                                                                       | 9 - Q2<br>B - R/W<br>7 - DB0<br>6 - DB1     | 1<br>2             | 01<br>RDY        | Phase 1 clock input. This clock input is<br>used to develop the internal overlapping<br>phase 2 clock. 1 MegHz or 2 MegHz<br>speeds.<br>Single step operation input. A low applied<br>will cause the processor to halt. The cur-<br>rent address line being fetched will be on<br>the address bug Open |

|   | A0-<br>A1-<br>A2-<br>A3-<br>A4-<br>A5-            | 6     34       7     34       8     33       9     32       10     31       11     30       12     29       13     28 | 4 DB3<br>3 DB4<br>2 DB5<br>DB6<br>DB7<br>P0 | 3                  | IRQ              | Interrupt request input. When a low pulse<br>is applied a jump to a location specified<br>by the contents of FFFE and FFFF will oc-<br>cur to service the interrupt if the interrupt                                                                                                                   |

|   | A7- 1<br>A8- 1<br>A9- 1                           | 13 28<br>14 27<br>15 26<br>16 25<br>17 24                                                                             | P2<br>P3<br>P4                              | 4                  | NMI              | Non-maskable interrupt input. A low tran-<br>sition will cause a jump to a location<br>specified by FFFA and FFFB to a subseque                                                                                                                                                                        |

|   | A11-1<br>A12-1                                    | 8 23                                                                                                                  | -A15<br>-A14                                | 5                  | <b>AEC</b>       | tine which will service the interrupt.<br>Address enable control input. A low ap-<br>plied to will cause the address bus to<br>enter hi impedance state, so other devices<br>can control the address bus.                                                                                              |

|   |                                                   |                                                                                                                       |                                             | 6<br>7-20<br>22,23 | VCC<br>A0-A15    | Address bus outputs. Unidirectional bus used to address memory and I/O deviace                                                                                                                                                                                                                         |

|   | A                                                 | PIN<br>SSIGNMENT                                                                                                      |                                             | 21<br>24-29        | GND<br>P0-P5     | trolling the AEC input.<br>Dc ground connection                                                                                                                                                                                                                                                        |

| i | -                                                 | 1 28<br>2 27<br>3 26                                                                                                  | –V <sub>CC</sub><br>–I8<br>–I9              |                    |                  | <ul> <li>I/O bidirectional port. This port can be controlled via memory locations 0000 and 0001.</li> <li>0001 = Output register</li> <li>0000 = Data dispute</li> </ul>                                                                                                                               |

|   | 15- 4<br>14- 5                                    | 4 25<br>5 24                                                                                                          | -l10<br>-l11                                | 30-37              | DBO-DB7          | 0000 = Data direction register<br>Bidirectional data bus. This is the bus that<br>passes the data to or from any I/O device<br>or memory.                                                                                                                                                              |

|   | 3-  6<br> 2-  7<br> 1-  8<br> 0-  9               | 22<br>21<br>21<br>20                                                                                                  | -l12<br>-l13<br>-l14<br>-l15                | 38                 | R/W              | Read/Write output. The processor gener-<br>ates a low level when writing, and a high<br>level when reading. This signal is usually<br>decoded for read or write operations to                                                                                                                          |

| 6 | F7- 10<br>F6- 11<br>F5- 12<br>F4- 13<br>SND- 14   | 18<br>18<br>17<br>16                                                                                                  | -CE<br>-F0<br>-F1<br>-F2                    | 39                 | 02               | Phase 2 output. The processor generates<br>this clock signal from the phase 1 clock<br>applied. The two clock signals are 180<br>degrees out of phase. The phase 2 dot                                                                                                                                 |

|   | U17                                               | 15<br>- 906114-01<br>GRAMMABLE                                                                                        | -F3                                         | 40                 | RES              | is used in decoding I/O and memory on<br>the positive half cycle.<br>Reset input interrupt. A low pulse causes<br>a jump to a subroutine specified by FFFC<br>and FFFD, which will initialize all proces-<br>sor controlled devices. This occurs during                                                |

|   | LOGIC                                             | C ARRAY (PLA)                                                                                                         |                                             |                    |                  | a power up sequence.                                                                                                                                                                                                                                                                                   |

i

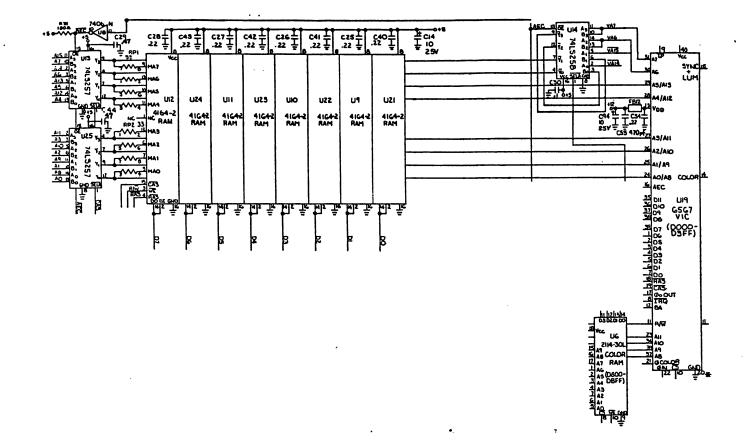

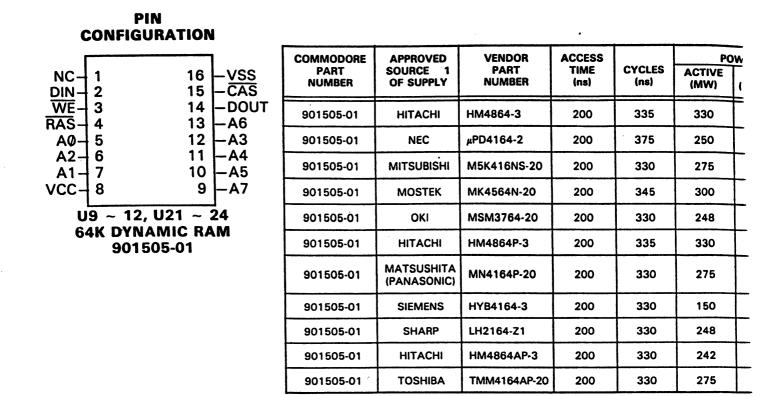

### **RAM Control Logic.**

U13 and U25 are multiplexers. The address outputs from the microprocessor are passed to RAM via U13 and U25 when the output Address Enable Control (AEC) from the VIC IC is "high". When AEC is "low" the VIC IC outputs refresh addresses on pins 24 - 31. AEC goes "low" when the system clock, phase 2, is "low". Since all I/O decoding occurs when phase 2 is "high", refresh is transparent to the processor.

Eight 4164 DRAMS provide 64k bytes of memory. One 2114 RAM (U6) provides 512 bytes of memory allocated for screen color data storage.

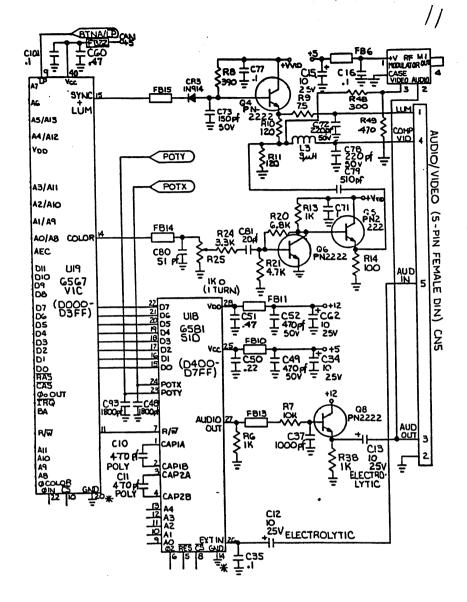

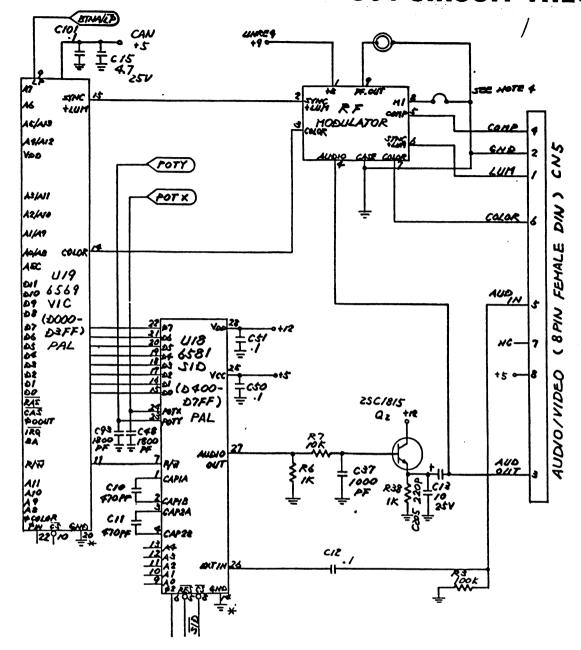

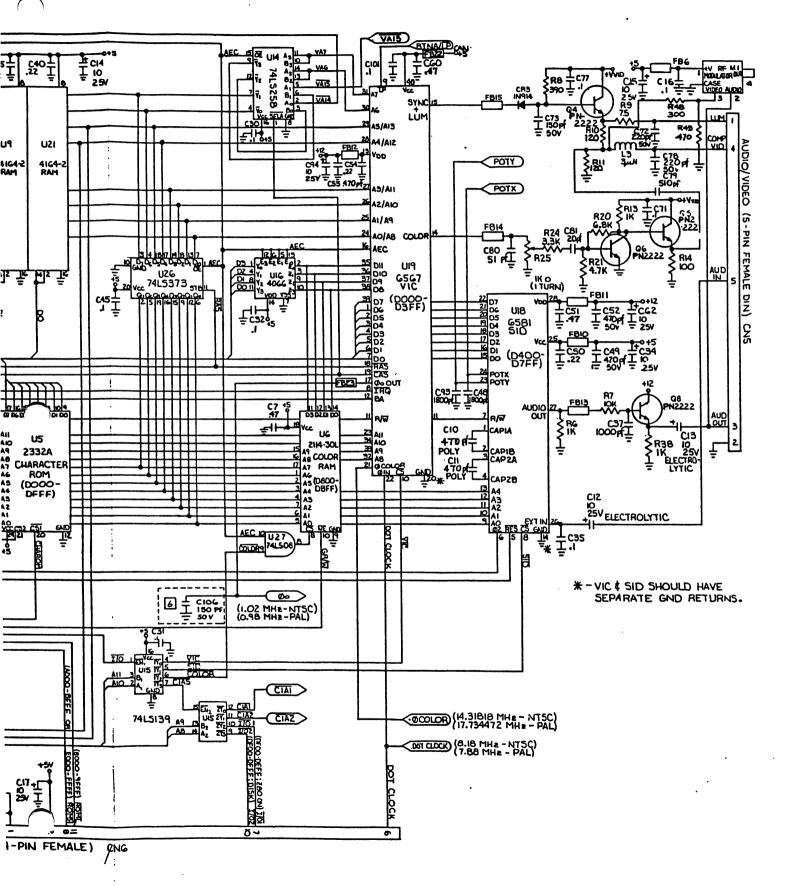

#### **5 Pin Video and Audio Output Circuits.**

Pin 15 of the VIC IC is the sync/luminance output. Pin 14 is the color output. A composite video output is created by mixing sync/luminance and color. The composite output is applied to the RF modulator, and also passed to the monitor connector CN5 on pin 4. The color output is not made available on the monitor connector CN5 as on the 8 pin version, and the RF modulator mixes audio with the composite video producing the TV RF output, unlike the 8 pin version RF modulator which creates the composite video output.

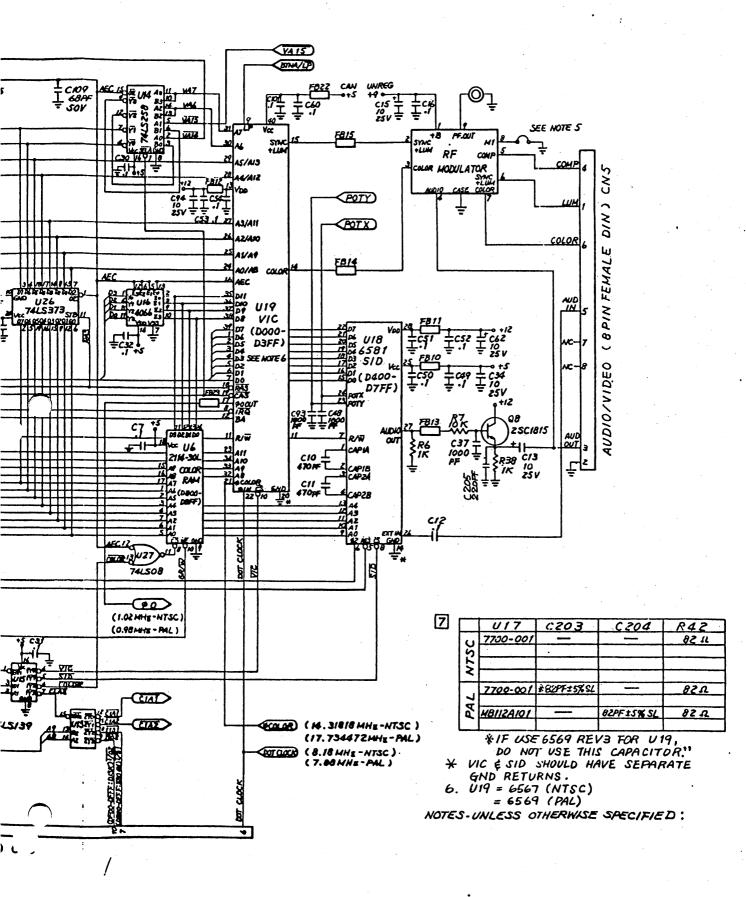

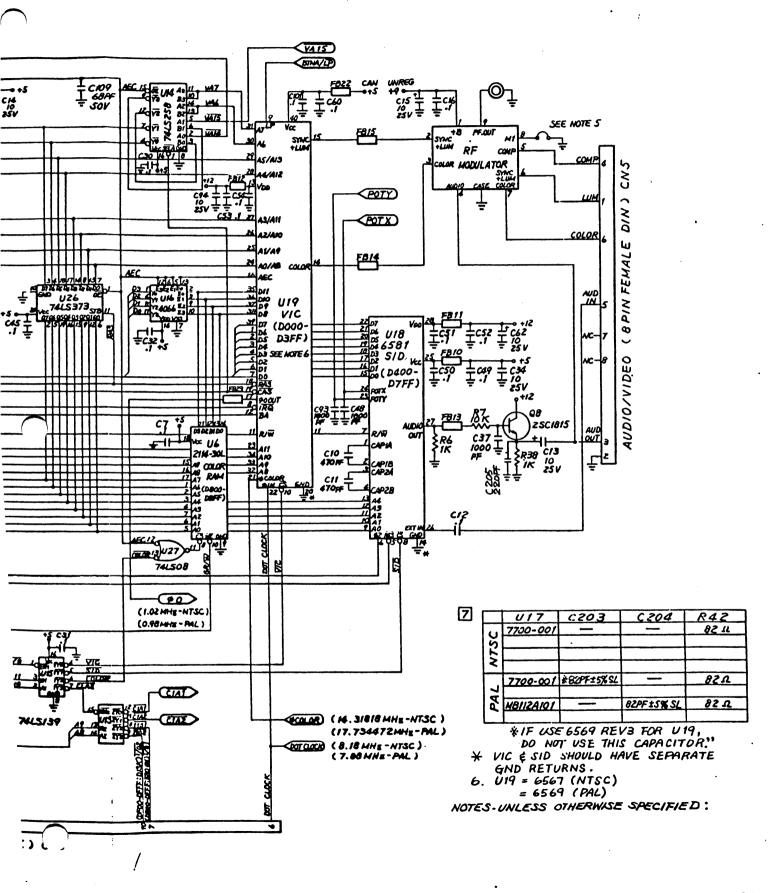

### 8 Pin Video and Audio Output Circuits. Refer to schematic 251469

:

U19 is the Video Interface Chip (VIC). Sync (horizontal and vertical), and luminance (video) is output on pin 15. This signal is passed to pin 2 of the RF modulator. Color is output on pin 14, and passed to pin 3 of the modulator. Light Pen inputs are sensed by the VIC IC on pin 9. U18 is the Sound Interface Device IC (SID). The audio output is on pin 27, and audio input is on pin 26. The RF modulator mixes sync/luminance, color, and audio out, generating a TV composite signal on pin 5. The RF modulator also passes the VIC outputs to the monitor connector CN5. Audio out on pin 27 is amplified by Q2, and output on pin 3 of CN5. Audio in is applied to pin 5 of CN5, then to pin 26 of the SID IC. Inputs from paddles connected to one of the control ports are monitored by the SID IC on pins 23 and 24.

А,

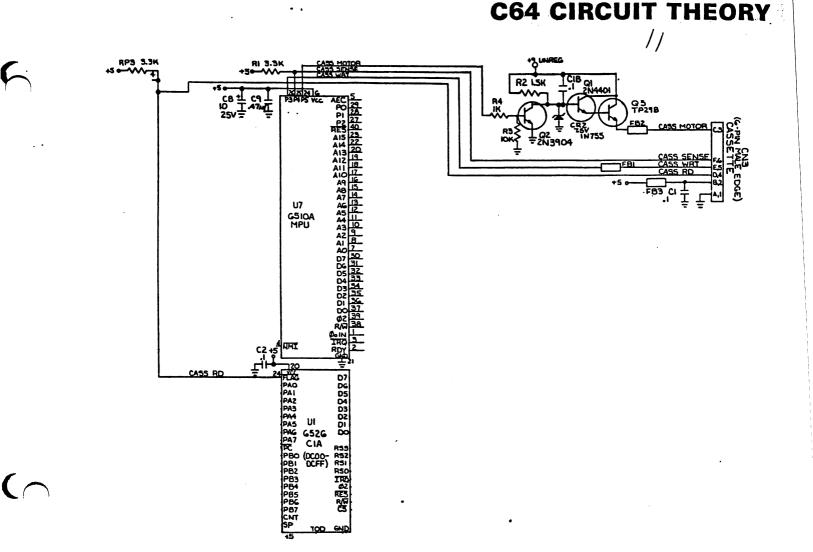

#### The Cassette Interface Circuits.

U7 is a 6510 microprocessor. One of the features of the 6510 is a built in parallel I/O port (P0-P5). P3 - P5 control most of the cassette interface circuitry. P3 pin 26 of U7 outputs the write data signal to connector CN3 on pins E and 5. P4 is an input that senses the play switch depressed on the cassette deck. P5 is an output that controls the cassette motor. When P5 goes "low", Q2 cuts off, CR2 regulates Vb of Q1 at 7.5 volts, this forward biases Q1 and Q3, passing current through the cassette motor coil. U1 is a Complex Interface Adapter (CIA). Parallel ports, serial outputs, and Timers are standard features of the CIA. Read data enters on pins D, 4 of CN3. U1 accepts the read data signal on the FLAG input pin 24.

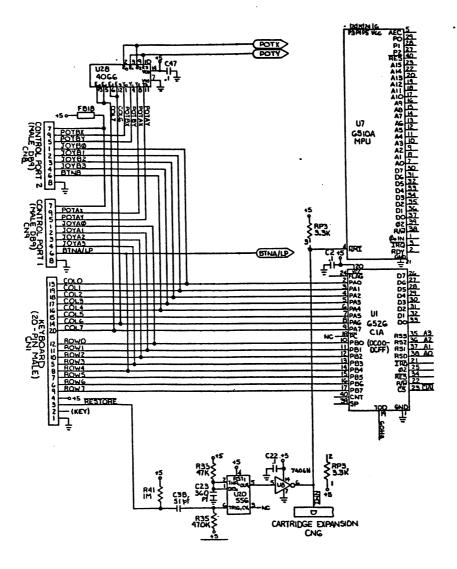

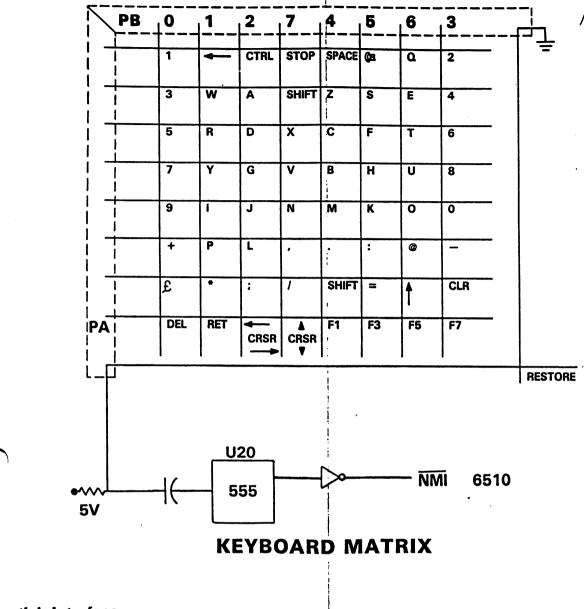

### Keyboard, Joystick, and Paddle Interface Circuits.

### **Keyboard Interface.**

U1 is a Complex Interface Adapter (CIA). Both parallel ports are used to decode the keyswitches on the keyboard. Parallel port A signals (PAO - PA7) are outputs. Parallel port B signals (PBO - PB7) are inputs. A "O" bit is shifted through the parallel port A, when a key is depressed on the keyboard, the "O" bit is returned on one of the parallel port B inputs. A program in the KERNAL ROM generates the shifting "O" bit output on parallel port A, and decodes the signals returning on the parallel port B inputs. Depressing the restore key causes U20 to trigger. U8 pin 6 goes "low" generating a Non-Maskable Interrupt (NMI) at the processor. This causes the processor to execute a subroutine which initializes the I/O Interfaces. If the STOP key is depressed at the same time, BASIC flags are also initialized.

# PARTS LIST - PCB ASSEMBLY #326298 (Continued)

Ý

/

215

{

C - Indicates Commodore Stocked Part Numbers

| CAPACITO      | DRS (Contine | (beu                                   | CAPACIT | CAPACITORS (Continued)                       |        |  |  |

|---------------|--------------|----------------------------------------|---------|----------------------------------------------|--------|--|--|

| C38           | Ceramic      | 51.pF, 50V                             | C94     | Electrolytic 10 µF, 25V, +50%                | 10     |  |  |

| C39           | Ceramic      | .1 μF, 50V                             | C95,96  | Ceramic $.1 \mu\text{F}$ , 50V               | •      |  |  |

| C40-43        | Ceramic      | .22 μF, 50V                            | C97     | Ceramic $.22 \ \mu\text{F}, 25\text{V}$      |        |  |  |

| C44           |              | .47 μF, 50V, 20%                       | C98,99  | Ceramic $.1 \ \mu\text{F}, 50\text{V}, 20\%$ |        |  |  |

| C45,46,47     |              | .1 μF, 50V, 20 λ                       | C100    | Ceramic $.22 \ \mu\text{F}, 25\text{V}$      |        |  |  |

| C48           | Ceramic      | 1800 pF, 50V                           | C101    | Ceramic $.1 \ \mu\text{F}, 50\text{V}, 20\%$ |        |  |  |

| C49           |              | 470 pF, 50V                            | C102    | Electrolytic 10 $\mu$ F, 25V, +50%           | - 10   |  |  |

| C50           |              | .22 μF, 50V                            | C102    | Ceramic $.1 \ \mu\text{F}$ , 50V             | , ,    |  |  |

| C51           |              | .47 μF, 50V, 20%                       | C105    | Ceramic $.1 \mu$ F, 50V                      |        |  |  |

| C52,53        | Ceramic      |                                        |         |                                              |        |  |  |

| C54           |              | .22 μF, 50V                            | CONNEC  | TORS                                         |        |  |  |

| C55           | Ceramic      | .1 μF, 50V                             |         | 1                                            |        |  |  |

| C56           |              | $.1 \ \mu F, 50V$                      | CN1     | Header Assy, 20 Pin 903                      | 3331-3 |  |  |

| C50<br>C57    |              | $10 \ \mu\text{F}, 25\text{V}, +50\%,$ | CN4     | 6 Pin Din C 90                               | 3361-( |  |  |

| C37           | Electrolytic | -10% $+50%$                            | CN5     | 5 Pin Din C 903                              | 3362-( |  |  |

| C58           | Commin       |                                        | CN6     | 44 Pin Card Edge C 90                        | 6100-  |  |  |

| C58<br>C59    | Ceramic      | .1 μF, 50V<br>.22 μF, 50V              | CN7     | 7 Pin Din C 90                               | 6130-  |  |  |

| C55<br>C60,61 |              | •                                      | CN8,9   | Plug Assy, 9 Pin Rt: Angle C 90              | 6126-  |  |  |

| C60,61<br>C62 |              | .47 μF, 50V, 20%                       | CN10    | Header Assy, 3 Pin                           |        |  |  |

| 62            | Electrolytic | 10 $\mu$ F, 25V, +50%,                 |         |                                              |        |  |  |

| 000           |              | -10%                                   |         | LANEOUS                                      |        |  |  |

| C63           |              | .47 μF, 50V, 20%                       |         |                                              |        |  |  |

| C64,65        | Electrolytic | 10 μF, 25V, +50%,                      | L1,2    |                                              | 1151-  |  |  |

|               |              | - 10%                                  | L3      |                                              | 1151-  |  |  |

| C66,67        |              | .47 μF, 50V, 20%                       | L4      |                                              | 6127-  |  |  |

| C68<br>C69    | Ceramic      | .1 μF, 50V                             | L5      | Coil Inductor 1.2 µH 90                      | 1152-  |  |  |

| C70           | Mica         | 10 pF, 500V, 5%                        | Y1      | . Crystal 14.31818 MHz C 90                  | 0558-  |  |  |

| C71           | Ceramic      | .1 μF, 50V                             |         |                                              |        |  |  |

| C72           | Ceramic      | 220 pF, 50V                            | SW1     | Rocker Switch DPDT C 90                      | 4500-  |  |  |

| C73           | Ceramic      | 150 pF, 50V                            | VR1     | Valaan Denvieten                             |        |  |  |

| C74           | Ceramic      | .1 μF, 50V                             |         | Voltage Regulator                            | 4007   |  |  |

| C77           | Ceramic      | .1 μF, 50V                             |         |                                              | 1527-  |  |  |

| C78           | Ceramic      | 220 pF, 50V                            | VR2     | Voltage Regulator                            |        |  |  |

| C79           | Ceramic      | 510 pF, 50V                            |         | MC7805CT 90                                  | 1527-  |  |  |

| C80           | Ceramic      | 51 pF, 50V                             | NA1     | Modulator C 32                               |        |  |  |

| C81           | Ceramic      | 20 pF, 50V                             |         |                                              | 6130   |  |  |

| C82           | Ceramic      | .1 μF, 50V                             | F1      | Fuse, Normal Blo, 250V, 1.5A                 |        |  |  |

| C83           | Mica         | 33 pF, 500V, 5%                        |         | 1 460, Horman Bio, 2007, 1.5A                |        |  |  |

| C84           | Ceramic      | .1 μF, 50V                             | FB1-23  | Ferrite Bead 90                              | 3025   |  |  |

| C85           | Ceramic      | .47 μF, 50V, 20%                       |         |                                              |        |  |  |

| C86           | Mica         | 39 pF, 500V, 5%                        |         | Connector Panel                              |        |  |  |

| C87           | Ceramic      | .1 μF, 50V                             |         | (ON, OFF, Joystick) 32                       | .6299  |  |  |

| C88           | Electrolytic | 470 μF, 50V                            |         |                                              | 26116  |  |  |

| C89           | Ceramic      | .1 μF, 50V                             |         |                                              | 26265  |  |  |

| C90           | Electrolytic | 470 μF, 50V                            | 11      |                                              | 26267  |  |  |

| C91           | Electrolytic | 100 μF, 16V                            |         |                                              |        |  |  |

| C92           | Ceramic      | .22 μF, 50V                            | 11      |                                              |        |  |  |

| C93           | Ceramic      | 1800 pF, 50V                           | 11      |                                              |        |  |  |

|               |              | 1000 p., 001                           |         | 1                                            |        |  |  |

:

### U1, U2 - 906108-01 6526 COMPLEX INTERFACE ADAPTER (CIA)

٠.,

.

PIN

|                      | PIN<br>ASSIGNM       | ENT                                                     | 1<br>2-9<br>10-17 | VSS<br>PAO-PA7<br>' PBO-PB7 | port.                                                                                                                                                                                   |

|----------------------|----------------------|---------------------------------------------------------|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND-                 | 1                    | 40 - CNT                                                | 18                | PC                          | Handshake output A low pulse is                                                                                                                                                         |

| PA0-<br>PA1-         | 2<br>3               | 39 – SP                                                 | 19                | TOD                         | generated after a read or write on port b.<br>Time of day clock input. Programmable                                                                                                     |

| PA2-                 | 4                    |                                                         | 20                | VCC                         | 50hz or 60hz input.<br>5VDC input.                                                                                                                                                      |

| PA3-<br>PA4-         | 5<br>6               | 36 - RS2                                                | 21                | IRQ                         | Interrupt output to microprocessor input                                                                                                                                                |

| PA5-<br>PA6-         | 7                    | 35 - RS3<br>34 - RES                                    | 22                | R/W                         | READ/WRITE input from microprocessor                                                                                                                                                    |

| PA7-                 | 8<br>9               | 33 – DBO<br>32 – DB1                                    | 23                | CS                          | Chip select input. A low pulse will as                                                                                                                                                  |

|                      | 11                   | 31 – DB2<br>30 – DB3                                    | 24                | FLAG                        | Negative edge sensitive interrupt insut                                                                                                                                                 |

| PB2-<br>PB3-<br>PB4- |                      | 29 – DB4<br>28 – DB5                                    | 25                | 02                          | either parallel port.<br>02 clock input. Connected to processor                                                                                                                         |

| PB5-<br>PB6-         | 15                   | 26 - DB7                                                | 26-33             | DBO-DB7                     | Bidirectional data bus. Connects to pro                                                                                                                                                 |

| PB7<br>PC<br>TOD     | 17<br>18<br>19<br>20 | 25 - 02<br>24 - FLAG<br>23 - CS<br>22 - R/W<br>21 - IRQ | 34<br>35-38       | res<br>RSO-RS3              | Low active reset input. Initializes CIA.<br>Register select inputs. Used to select all<br>internal registers for communications with<br>the parallel ports, time of day clock and       |

| L                    |                      |                                                         | 39                | SP                          | Serial Port bidirectional connection. An in-<br>ternal shift register converts microarce                                                                                                |

|                      |                      |                                                         | 40                | CNT                         | cessor parallel data into serial data, and<br>visa-versa.<br>Count input. Internal timers can count<br>pulses applied to this input. Can be used<br>for frequency dependent operations. |

### U18 - 906112-01 **6581 SOUND INTERFACE** DEVICE (SID)

| ASSIG<br>CAP- 1A<br>CAP- 1B<br>CAP- 2A<br>CAP- 2B<br>RES- 5<br>02- 6<br>R/W- 7<br>CS- 8<br>A0- 9<br>A1- 10<br>A2- 11<br>A3- 12<br>A4- 13<br>GND- 14 | 28 - 12V<br>27 - A.OUT<br>26 - EXT IN<br>25 - 5V<br>24 - POT X<br>23 - POT Y<br>22 - D7<br>21 - D6<br>20 - D5<br>19 - D4<br>18 - D3<br>17 - D2<br>16 - D1<br>15 - D0 | 1,2,<br>3,4<br>5<br>6<br>7<br>8<br>9-13<br>14<br>15-22<br>23<br>24<br>25<br>26<br>27<br>28 | DO-D7<br>POT Y<br>POT X<br>VCC<br>EXT IN<br>Audio out | Capacitor filter connections.<br>Reset input. A low pulse initializes the<br>SID.<br>Processor phase 2 clock input.<br>Processor read/write input.<br>Chip select input.<br>Address lines from processor.<br>Dc ground connection.<br>Data Bus connections.<br>Input to a A/D converter used to detect<br>the value of a variable resistor. Commonly<br>connected to game paddles.<br>Same as POT Y.<br>5VDC.<br>External audio input.<br>Audio output. Should be AC coupled to<br>audio amp. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                     |                                                                                                                                                                      | 20                                                                                         | Vdd                                                   | 12VDC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

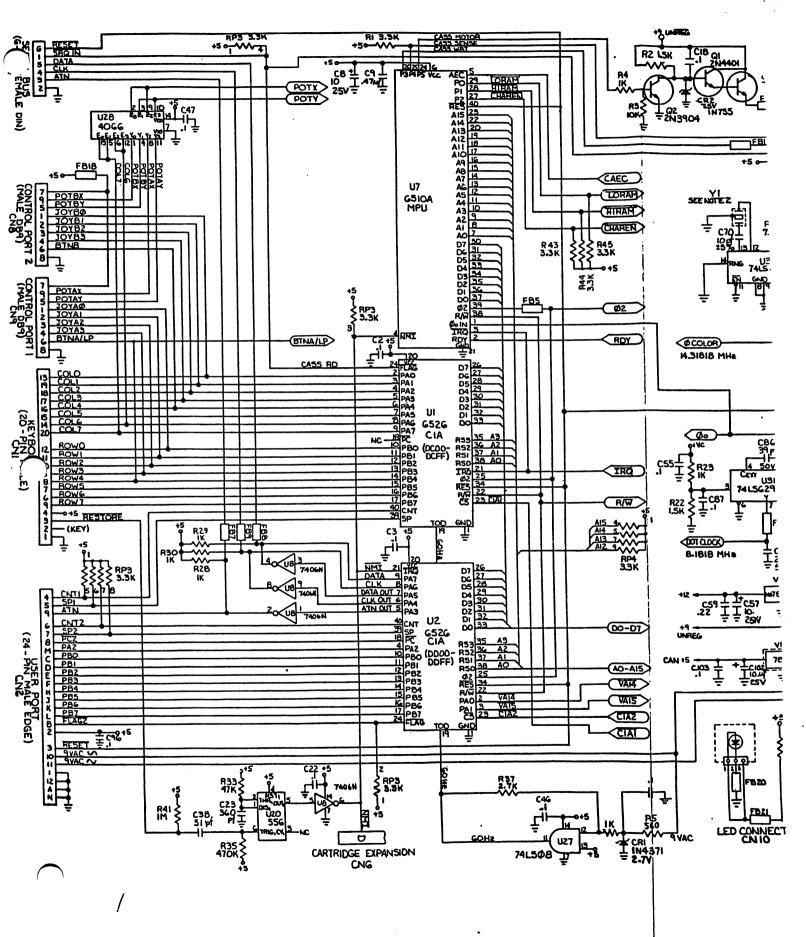

# SCHEMATIC #326106 SHEET 1 OF 2

ينيو ويتركز ما

۰.

•

S

| Y              |                                                                                      |  |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| POWER          |                                                                                      |  |  |  |  |  |  |  |

| ACTIVE<br>(MW) | STANDBY<br>(MAX)(MW)                                                                 |  |  |  |  |  |  |  |

| 330            | 20                                                                                   |  |  |  |  |  |  |  |

| 250            | 28                                                                                   |  |  |  |  |  |  |  |

| 275            | 28                                                                                   |  |  |  |  |  |  |  |

| 300            | 22                                                                                   |  |  |  |  |  |  |  |

| 248            | 23                                                                                   |  |  |  |  |  |  |  |

| 330            | 20                                                                                   |  |  |  |  |  |  |  |

| 275            | 27.5                                                                                 |  |  |  |  |  |  |  |

| 150            | 20                                                                                   |  |  |  |  |  |  |  |

| 248            | 28                                                                                   |  |  |  |  |  |  |  |

| 242            | 20                                                                                   |  |  |  |  |  |  |  |

| 275            | 22                                                                                   |  |  |  |  |  |  |  |

|                | ACTIVE<br>(MW)<br>330<br>250<br>275<br>300<br>248<br>330<br>275<br>150<br>248<br>242 |  |  |  |  |  |  |  |

**ODIN**

---> DOUT

-∘vcc

-∞vss

RATOR

Stream.

н<sup>°</sup>

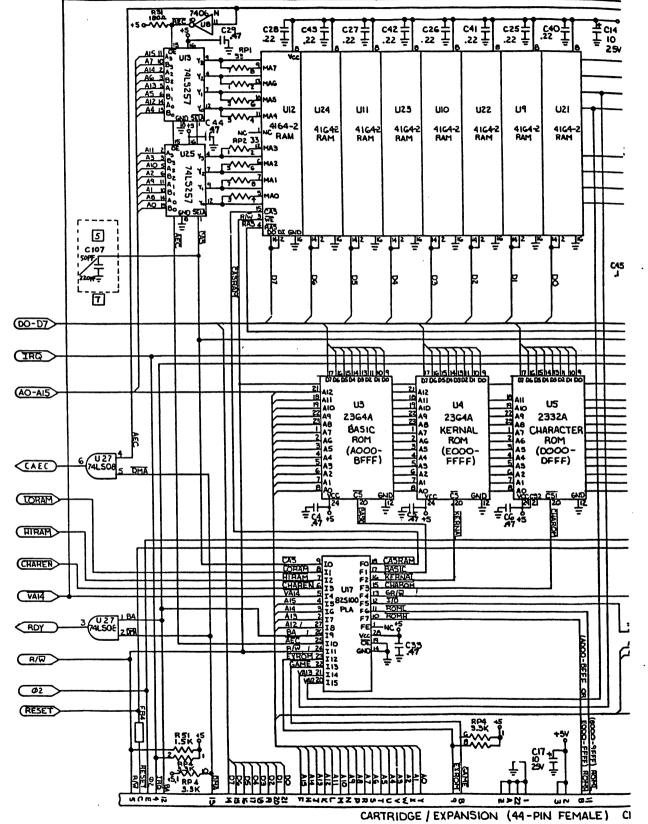

# SCHEMATIC #326106 SHEET 2 OF 2

(

•

ভি

i,

IS SUITABLE FOR MBITZATO

CZOC. IT

77

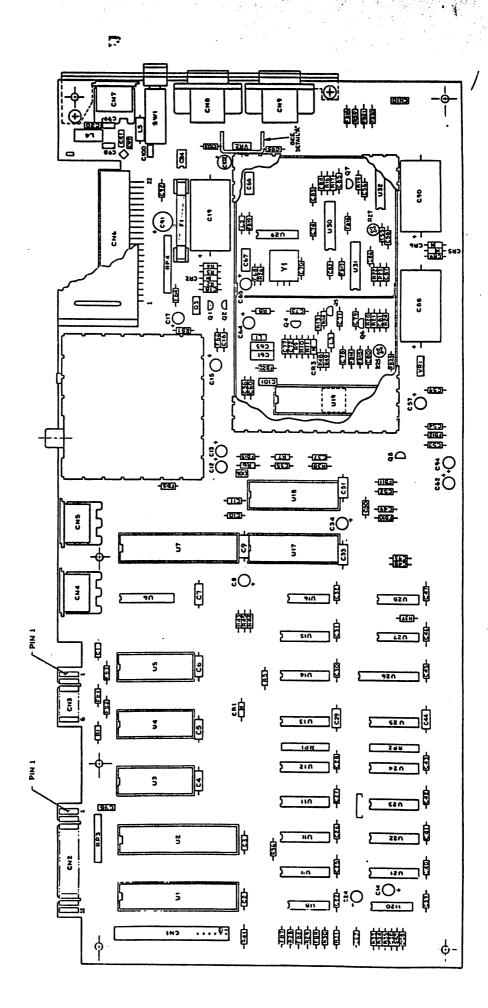

**BOARD LAYOUT #250407-04**

### PARTS LIST - PCB ASSEMBLY #250407-04

.

**C** – Indicates Commodore Stocked Part Number

| INTEGRA                     | TED CIRCUITS        |                  | RESISTOR         | S (Continue  | d)         |                  |        |       |

|-----------------------------|---------------------|------------------|------------------|--------------|------------|------------------|--------|-------|

| U1,U2                       | 6526 CIA            | C 906108-01      | R26              | Jumper Wire  |            | R39              | 390    | )     |

| U3                          | 2364 Basic ROM      | C 901226-01      | R27              | Pot 500Ω     | - 11       | R41              | 1M     |       |

| U4                          | 2364 Kernal ROM     | C 901227-03      | R28              | 1K           |            | R42              | 82     |       |

| U5                          | 2332 Char ROM       | C 901225-01      | R29              | 1K           |            | R43              | 3.3    | κ     |

| U6                          | 2114L-20 RAM        | 901453-01        | R30              | 1K           |            | R44              | 3.3    | κ     |

| U7                          | 6510 μ Processor    | C 906107-01      | R31              | 180          |            | R45              | 3.3    | К     |

| U8                          | 7406                | 901522-06 sub:   | R33              | 47K          |            | R50              | 1M     |       |

|                             | 7416                | 901522-14        | R34              | 47K          |            | R51              | 1.5    | К     |

| U9-U12                      | 4164 (200 nS)       | 901505-01        | R35              | 470K         |            | R52              | 300    | )     |

| U13                         | 74LS257             | 901521-57        | <sup>,</sup> R36 | 1K           |            | R53              | 390    | )     |

| U14                         | 74LS258             | 901521-58        | R37              | 2.7K         |            | R100             | 1K     |       |

| U15                         | 74LS139             | 901521-18        | R38              | 1K           |            | R101             | 22     | <     |

| U16                         | 4066                | 901502-01        |                  |              | L          |                  |        |       |

| U17                         | 82S100 PLA          | C 906114-01      | RESISTOR         | R PACKS      |            |                  |        |       |

| U18                         | 6581 SID            | C 906112-01      | RP1,2            | 220 9 Bin (  | Daure      |                  |        |       |

| U19                         | 6567 VIC II         | C 906109-04      | RP1,2            | 33Ω, 8 Pin ( |            | ns ino.          |        |       |

| U20                         | LM556               | 901523-03        | 000              | 4308R-102-   |            |                  |        |       |

| U21-U24                     | 4164 (200 nS)       | 901505-01        | RP3              | 3.3KΩ, 8 Pir |            | urns No.         |        |       |

| U25                         | 74LS257             | 901521-57        | 004              | 4308R-101-   |            |                  |        |       |

| U26                         | 74LS373             | 901521-29        | RP4              | 3.3KΩ, 10 F  | 'n         |                  |        |       |

| U27                         | 74LS08              | 901521-03        | CAPACIT          | ORS          |            |                  |        |       |

| U28                         | 4066                | 901502-01        |                  |              |            | ·····            |        |       |

| U29                         | 74LS74              | 901521-06        | C1-7             | Ceramic      | .1         | μF, 25V          |        |       |

| U30                         | 74LS193             | 901521-26        | C8               | Electrolytic |            | μF, 25V,         | + 50%. | - 109 |

| U31                         | 74LS629             | 901521-68        | C9               | Ceramic      |            | μ <b>F</b> , 25V |        | • - · |

| U32                         | MC4044              | 906128-01        | C10,11           | Ceramic      |            | ) pF, 50V,       | 10%    |       |

|                             |                     |                  | C12              | Ceramic      |            | μ <b>F</b> , 25V |        |       |

| TRANSIS                     | TORS                |                  | C13,14,15        | Electrolytic | 10         | μF, 25V,         | + 50%, | - 109 |

| Q1,2                        | 2SC1815             | C 902693-01 sub: | C16              | Ceramic      |            | μF, 25V          |        |       |

| 03                          | TIP29 A             | 902653-01        | C17              | Electrolytic |            | )μF, 25V,        | + 50%, | - 109 |

| Q7,8                        | 2SC1815             | C 902693-01      | C18              | Ceramic      |            | Ι μF, 25V        |        |       |

|                             | 1                   |                  | C19              | Electrolytic |            | •                |        |       |

| DIODES                      |                     |                  | C20,21           | Film         |            | 2 μF, 100V,      | , 20%  |       |

|                             |                     |                  | C22              | Ceramic      |            | μ <b>F</b> , 25V |        |       |

| CR1                         | 2.7V Zener IN4371   |                  | C23              | Ceramic      |            | ) pF, 50V,       |        |       |

| CR2                         | 7.5V Zener IN755    | 900941-01        | C24              | Electrolytic |            | ) μF, 25V,       | +50%,  | -109  |

| CR4                         | Bridge S2VB10       | C 251026-01      | C25-33           | Ceramic      |            | 1 μF, 25V        |        |       |

|                             | DBA20B              | C 251026-02      | C34              | Electrolytic |            | D μF, 25V,       | + 50%, | - 109 |

|                             | DBA20C              | C 251026-03      | C35              | Ceramic      |            | 1 μF, 50V        |        |       |

| CR5,6                       | Rectifier IN4001    | 900750-01        | C36              | Ceramic      |            | ) pF, 50V,       |        |       |

| RESISTO                     | RS – All values are | in ohms- 1/4 W   | C37              | Ceramic      |            | ) pF, 50V,       |        |       |

| 5%, unless noted otherwise. |                     | C38              | Ceramic          |              | 1 pF, 50V, | 5% SL            |        |       |

|                             |                     |                  | C39-47           | Ceramic      |            | 1 μF, 25V        |        |       |

| R1                          | 3.3K R6             | 1K               | C48              | Ceramic      |            | ) pF, 50V,       | 10% B  |       |

| R2                          | 1.5K R7             | 10K              | C49-54           | Ceramic      |            | 1 μF, 25V        |        |       |

| R3                          | 10K R16             | 1K               | C55              | Ceramic      |            | 1 μF, 50V        |        |       |

| R4                          | 1K   R17            | 2.7K             | C56              | Ceramic      |            | 1 μF, 25V        |        |       |

| R5                          | 560 R19             | 15K              | C57              | Electrolytic |            | 0 μF, 25V,       | + 50%, | - 10  |

|                             |                     |                  | C58              | Ceramic      | •          | 1 μF, 50V        |        |       |

### PARTS LIST — PCB ASSEMBLY #250407-04 (Continued)

(

| CAPACITO         | ORS (Contin  | ued)                                  | CONNEC               | rors .                                        |                                         |  |  |  |

|------------------|--------------|---------------------------------------|----------------------|-----------------------------------------------|-----------------------------------------|--|--|--|

| C59,60<br>C62,65 |              | _1 μF, 25V<br>10 μF, 25V, +50<br>–10% | 6, CN1<br>CN4<br>CN5 | Header Assy, 20 Pin<br>6 Pin Din<br>8 Pin Din | 903331-20<br>C 903361-01<br>C 325573-01 |  |  |  |

| C66,67,68        | Ceramic      | .1 μF, 25V                            | CN6                  | 44 Pin Card Edge                              | C 906100-02                             |  |  |  |

| C70              | Film         | 16 pF, 5%                             | CN7                  | 7 Pin Din                                     | C 251116-01                             |  |  |  |

| C74,82           | Ceramic      | .1 μ <b>F, 25</b> V                   | CN8,9                | Plug Assy, 9 Pin MINID                        | C 906126-01                             |  |  |  |

| C83              | Ceramic      | 82 pF, 5%                             | CN10                 | Header Assy, 3 Pin                            | 903332-03                               |  |  |  |

| C84              | Ceramic      | .1 μF, 25V                            |                      |                                               |                                         |  |  |  |

| C85              | Ceramic      | .47 μF, 50V, 10%                      | MISCELI              | MISCELLANEOUS                                 |                                         |  |  |  |

| C88              |              | 1000 μF, 25V                          | L2                   | Coil Inductor 2.2 µH                          | 901151-17                               |  |  |  |

| C89              | Ceramic      | .1 μF, 25V                            |                      | Coil Inductor 1.2 $\mu$ H                     |                                         |  |  |  |

| C90              |              | 470 μF, 50V                           |                      | Choke Coil                                    | C 325559-02                             |  |  |  |

| C91              | Electrolytic | 100 μF, 16V, +50                      | %,    ===            |                                               | 0 020000 02                             |  |  |  |

|                  |              | - 10%                                 | Y1                   | Crystal 14.31818 MHz                          | C 900558-01                             |  |  |  |

| C92              | Ceramic      | .1 μF, 25V                            |                      |                                               |                                         |  |  |  |

| C93              | Ceramic      | 1800 pF, 50V, 109                     |                      | Rocker Switch DPDT                            | 904500-01                               |  |  |  |

| C94              | Electrolytic | • • •                                 | %,                   |                                               |                                         |  |  |  |

|                  |              | - 10%                                 | VR1                  | Voltage Regulator                             |                                         |  |  |  |

| C95,96           | Ceramic      | .1 μF, 25V                            |                      | MC7812CT                                      | 901527-01                               |  |  |  |

| C97              |              | .22 μF, 25V                           | VR2                  | Voltage Regulator                             |                                         |  |  |  |

| C98,99           | Ceramic      | .1 μF, 50V, +8                        | %,                   | MC7805CT                                      | 901527-02                               |  |  |  |

|                  |              | - 20%                                 |                      |                                               |                                         |  |  |  |

| C100             | Ceramic      | .22 μF, 25V                           | M1                   | Modulator                                     | C 251080-01                             |  |  |  |

| C101             | Ceramic      | .1 μF, 50V, +8                        | %,   <br>   F1       |                                               | 4 5 4                                   |  |  |  |

|                  | _            | -20%                                  |                      | Fuse, Normal Blo, 250V,                       | , 1.5A                                  |  |  |  |

| C102             | Electrolytic | 10 μF, 25V, +5<br>- 10%               | %, FB1-5             | Ferrite Bead                                  | 903025-01                               |  |  |  |

| C103             | Ceramic      | - 10%<br>.1 μF, 25V                   | FB7-23               |                                               |                                         |  |  |  |

| C103             | Ceramic      | .ι μ⊨, 20 <b>ν</b>                    |                      |                                               |                                         |  |  |  |

| C104             | Ceramic      | .1 μ <b>F, 25</b> V                   |                      | Connector Panel                               |                                         |  |  |  |

| C108             |              | 10 μF, 25V, 209                       |                      | (Power, ON, OFF)                              |                                         |  |  |  |

| C200             | Ceramic      | .1 μF, 25V                            |                      | Cartridge Guide                               | 326116-01                               |  |  |  |

|                  |              |                                       |                      |                                               | C 251023-01                             |  |  |  |

|                  | ļ            |                                       |                      | Shield Cap                                    | C 251024-01                             |  |  |  |

:

# C — Indicates Commodore Stocked Part Number

!

/

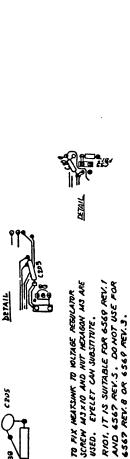

**MODULATOR SCHEMATIC #251025**

:

: S 4

CARTRIDGE/EXPANSION (44 PIN FEMALE) CN6

SCHEMATIC #251138 SHEET 1 OF 2

SCHEMATIC #251138 SHEET 1 OF 2

### U7 — 906107-01 6510 Microprocessor

ZCIZ

•

٠d

n

e

C-

pt

ЭS

;

d

зt

e

# SCHEMATIC #251138 SHEET 2 OF 2

BOARD LAYOUT #250425-01

DETAIL 'C' SOUND CARRIER SELECT

|        |                   | OW            | MODULATOR          |                   |               |

|--------|-------------------|---------------|--------------------|-------------------|---------------|

| annos  |                   |               | PAL                | 76                |               |

| SEVERT | NTSC              | P.M 251025-01 | 025-01             | P/N 251697-01     | 10-265        |

|        |                   | -02 (GER)     | -02 (GER) -03 (UK) | -02(GER) -03 (    | -03 (UK)      |

| JUMPER | DON'T CARE OPEN   |               | TAOR2              | DON'T             | DOW'T<br>CARE |

| SWITCH | SWITCH DON'T CARE | DON'T         | DOWT               | POSITION LOUTISON | POSITION      |

:

### PARTS LIST - PCB ASSEMBLY #250425-01

C - Indicates Commodore Stocked Part Number

| INTEGRAT                                          |               | rs         |                | RESISTOR   | S (Continue             | d)                      |                          |          |            |

|---------------------------------------------------|---------------|------------|----------------|------------|-------------------------|-------------------------|--------------------------|----------|------------|

| U1,U2                                             | 6526 CIA      | · .        | C 906108-01    | R39        | 390                     |                         | R50                      | 1M       |            |

| U3                                                | 2364 Basic F  |            | C 901226-01    | R41        | 1M                      |                         | R51                      | 1.5      |            |

| U4                                                | 2364 Kernal   |            | C 901227-03    | R42        | 82                      |                         | R60                      | 100      | 1          |

| U5                                                | 2332 Char R   | OM         | C 901225-01    | R43        | 3.3K                    |                         | R100                     | 1K       |            |

| U6                                                | 2114L-20 R/   | M          | 901453-01      | R44        | 3.3K                    |                         | R101                     | 22K      |            |

| U7                                                | 6510 µ Proc   | essor      | C 906107-01    | R45        | 3.3K                    |                         |                          |          |            |

| U8                                                | 7406          |            | 901522-06 sub: | <u> </u> 4 |                         | I                       | · · · ·                  | I        |            |

|                                                   | 7416          |            | 901522-14      | RESISTOR   | PACKS                   |                         |                          |          |            |

| U9-U12                                            | 4164 (200 r   | IS)        | 901505-01      |            |                         |                         |                          |          |            |

| U13                                               | 74LS257       | •          | 901521-57      | RP1,2      | 33Ω, 8 Pin (            |                         |                          |          |            |

| U14                                               | 74LS258       |            | 901521-58      |            | 4308R-102-              |                         |                          |          |            |

| U15                                               | 74LS139       |            | 901521-18      | RP3        | 3.3KΩ, 8 Pi             |                         |                          |          |            |

| U16                                               | 4066          |            | 901502-01      |            | 4308R-101-              |                         |                          |          |            |

| U17                                               | 82S100 PLA    |            | C 906114-01    | RP4        | 3.3KΩ, 10 F             | Pin, 1                  | /4 W                     |          |            |

| U18                                               | 6581 SID      | •          | C 906112-01    | RP5        | 1KΩ, 6 Pin              |                         |                          |          |            |

| U19                                               | 6567 VIC II   |            | C 906109-04    | CAPACIT    | APC                     |                         |                          |          |            |

| U20                                               | LM556         |            | 901523-03      | CAPACIT    | UN3                     |                         |                          |          |            |

| U21-U24                                           | 4164 (200 r   | nS)        | 901505-01      | C1-7       | Ceramic                 | 1                       | Ι μF, 25V                |          |            |

| U25                                               | 74LS257       | ,          | 901521-57      | C9         | Ceramic                 |                         | 1 μF, 25V                |          |            |

| U26                                               | 74LS373       |            | 901521-29      | C10,11     | Ceramic                 |                         | •                        | 10%      |            |

| U27                                               | 74LS08        |            | 901521-03      | C12        |                         |                         |                          |          |            |

| U28                                               | 4066          |            | 901502-01      | C12        | Ceramic<br>Electrolytic | . 10                    | $\mu_1, 25V$             | ± 50%    | _ 10       |

| U31                                               | 7701/8701     |            | C 251527-01    | C15        | Tantalum                |                         | 7 μF, 16V,               |          | - 10       |

| 001                                               | //01/07/01    |            | C 231327-01    | C19        | Electrolytic            |                         | • • •                    | 20%      |            |

| TRANSISTORS                                       |               |            | C10<br>C20     |            |                         | 2 μF, 100<br>2 μF, 100V | 20%                      |          |            |

|                                                   | 1             |            |                | C22        | Ceramic                 |                         | 1 μF, 25V                | , 20 /0  |            |

| Q1                                                | TIP29 A       |            | 902653-01      | C23        | Ceramic                 |                         | ο pF, 50V,               | 10% sut  | <b>.</b> . |

| Q2-4                                              | 2SC1815       |            | C 902693-01    | 020        | Geraine                 |                         | 5 pf, 001,<br>5 pF       | 1070 00. |            |

| DIODES                                            | •             |            |                | C24        | Electrolytic            |                         | 2 μF, 25V,               | +50%,    | - 10       |

|                                                   | 1             |            |                | C31,33,34  |                         |                         | 1 μF, 25V                |          |            |

| CR1                                               | 2.7V Zener    | IN4371     | 906103-02      | C37        | Ceramic                 | 1000                    | ) pF, 50V,               | 10% B    |            |

| CR2                                               | 6.8V Zener    | IN754A     |                | C38        | Ceramic                 | 5                       | 1 pF, 50V,               | 5% SL    |            |

| CR4                                               | Bridge S2V3   | 810 C      | 251026-01 sub: | C39-46     | Ceramic                 | •                       | 1 μF, 25V                |          |            |

|                                                   | DBA           | 20B C      | 251026-02 sub: | C48        | Ceramic                 |                         | 0 pF, 50V,               |          |            |

|                                                   | DBA           | 20C        | C 251026-03    | C50,51,53  | Ceramic                 | •                       | 1 μF, 25V                |          |            |

| CR5,6                                             | Rectifier IN4 | 001        | 900750-01      | C59        | Ceramic                 |                         | 1 μF, 25V                |          |            |

| CR9,                                              | IN4           | 148 sub    |                | C88        | Electrolytic            |                         |                          |          |            |

| CR12-16,                                          |               |            |                | C90        | Electrolytic            |                         | 0 μF, 50V                |          |            |

| 100-105                                           |               | 14         |                | C91        | Electrolytic            |                         | 0 μF, 16V,               | + 50%,   | - 10       |

|                                                   | 1             |            |                | C93        | Ceramic                 |                         | 0 pF, 50V,               | •        |            |

| <b>RESISTORS</b> – All values are in ohms- 1/4 W, |               |            | C101           | Ceramic    |                         | 1 μF, 50V,              |                          | - 20     |            |

|                                                   | 5%, u         | nless note | ed otherwise.  | C102       | Ceramic                 |                         | 1 μF, 25V                |          | - `        |

|                                                   |               |            |                | C150-152   | 1                       |                         | 0 pF, 50V,               | 10%      |            |

| R1                                                | 3.3K          | R26        | 3.3K           | C153       | Ceramic                 |                         | 8 pF, 50V,               |          |            |

| R2                                                | 470           | R31        | 180            | C154       | Ceramic                 |                         | 0 pF, 50V,               |          |            |

| R3                                                | 100K          | R33        | 47K            | C200       | Ceramic                 |                         | 1 μF, 25V                |          |            |

| R4                                                | 1K            | R34        | 47K            | C200       | Ceramic                 |                         | ο pF, 50V,               |          |            |

| R5                                                | 560           | R35        | 470K           | C204       | Ceramic                 |                         | 0 pF, 50V,<br>0 pF, 50V, |          |            |

| R6                                                | 1К            | R37        | 2.7K           |            |                         | 22                      | o hu, 200'               | , 370    |            |

| R7                                                | 10K           | R38        | 1K             | CT1        | Trimmer                 | 4                       | 0 pF                     |          |            |

29

語行手

11

(

### PARTS LIST. - PCB ASSEMBLY #250425-01 (Continued)

4

: :

(

# C – Indicates Commodore Stocked Part Number

| CONNEC                                           | TORS                                                                                                                           |                                                                                                   | MISCELLANEOUS (Continued) |                                                                                      |                                     |  |  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------|-------------------------------------|--|--|

| CN1<br>CN4<br>CN5<br>CN6<br>CN7<br>CN8,9<br>CN10 | Header Assy, 20 Pin<br>6 Pin Din<br>8 Pin Din<br>44 Pin Card Edge<br>7 Pin Din<br>Plug Assy, 9 Pin MINID<br>Header Assy, 3 Pin | 903331-20<br>C 903361-01<br>C 325573-01<br>C 906100-02<br>C 251116-01<br>C 251057-01<br>903332-03 | SW1<br>VR1<br>VR2         | Rocker Switch DPDT<br>Voltage Regulator<br>MC7812CT<br>Voltage Regulator<br>MC7805CT | 904500-01<br>901527-01<br>901527-02 |  |  |

| MISCELLANEOUS                                    |                                                                                                                                |                                                                                                   | M1                        | Modulator                                                                            | C 251696-01                         |  |  |