# SERVICE MANUAL

# **MODEL C-128 COMPUTER**

# Preliminary

# AUGUST 1985 PN-314001-07

#### Commodore Business Machines, Inc.

1200 Wilson Drive, West Chester, Pennsylvania 19380 U.S.A.

Commodore makes no expressed or implied warranties with regard to the information contained herein. The information is made available solely on an as is basis, and the entire risk as to quality and accuracy is with the user. Commodore shall not be liable for any consequential or incidental damages in connection with the use of the information contained herein. The listing of any available replacement part herein does not constitute in any case a recommendation, warranty or guaranty as the quality or suitability of such replacement part. Reproduction or use without expressed permission, of editorial or pictorial content, in any matter is prohibited.

This manual contains copyrighted and proprietary information. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission of Commodore Electronics Limited.

Copyright © 1985 by Commodore Electronics Limited. All rights reserved.

# CONTENTS

| Title                                   | Page |

|-----------------------------------------|------|

| SPECIFICATIONS                          | 1    |

| PARTS LIST                              | 2    |

| BLOCK DIAGRAM                           | 3    |

| THEORY                                  |      |

| BUS ARCHITECTURE                        | 4    |

| 8502 MICROPROCESSOR                     | 6    |

| Z-80 MICROPROCESSOR                     | 8    |

| MEMORY ARCHITECTURE                     | 11   |

| READ ONLY MEMORY                        | 15   |

| RANDOM ACCESS MEMORY                    | 17   |

| MEMORY MANAGEMENT UNIT                  | 20   |

| PROGRAMMED LOGIC ARRAY                  | 28   |

| 8701 CLOCK GENERATOR                    | 30   |

| VIDEO INTERFACE                         | 31   |

| 8564 VIDEO INTERFACE CHIP               | 33   |

| 8563 VIDEO CONTROLLER                   | 36   |

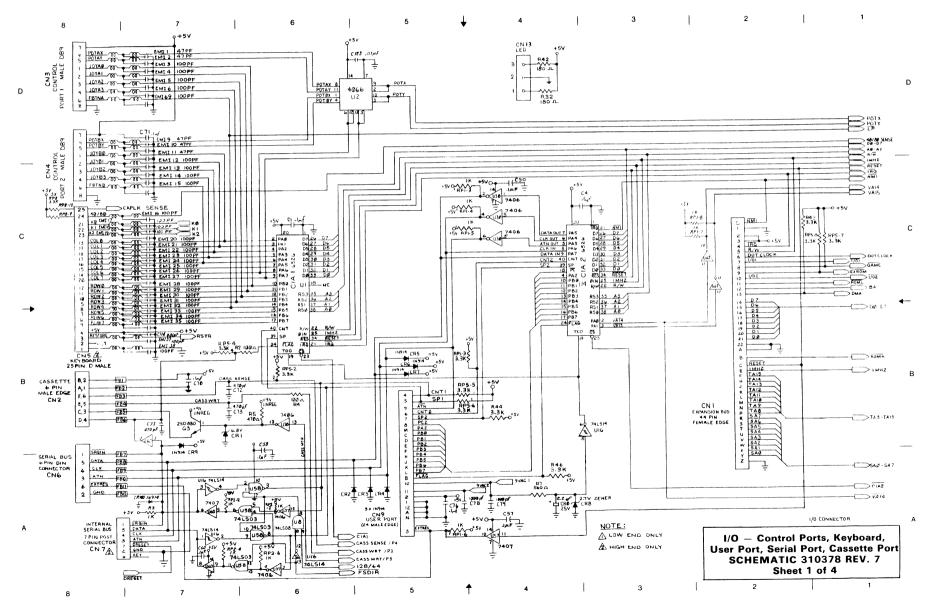

| I/O — INPUT/OUTPUT CIRCUITS             | 39   |

|                                         | 39   |

| CASSETTE INTERFACE                      |      |

|                                         | 41   |

| EXPANSION BUS                           | 42   |

| SERIAL BUS                              | 44   |

| TROUBLESHOOTING                         |      |

| COMMON LINE DEFINITIONS                 | 46   |

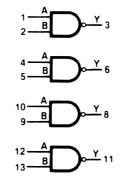

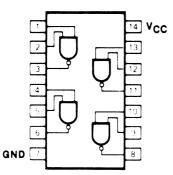

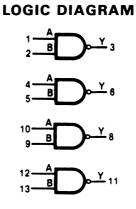

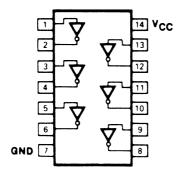

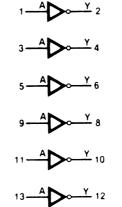

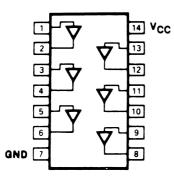

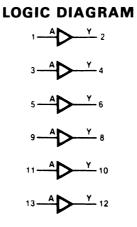

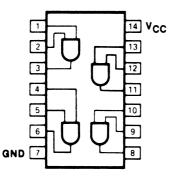

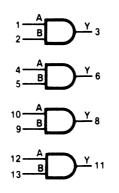

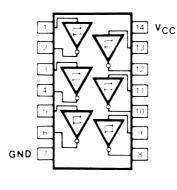

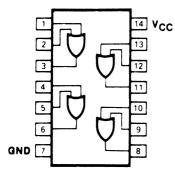

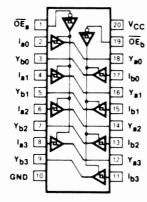

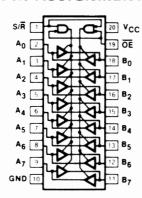

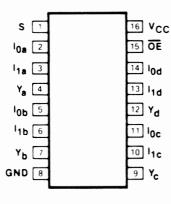

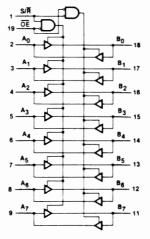

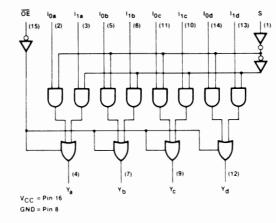

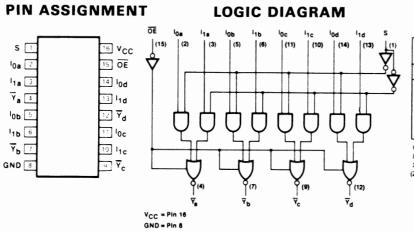

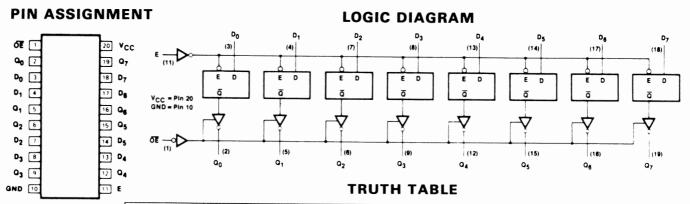

| COMMON I.C.'S (PIN ASSIGNMENTS & LOGIC) | 47   |

| INITIAL SERVICE POLICY                  | 53   |

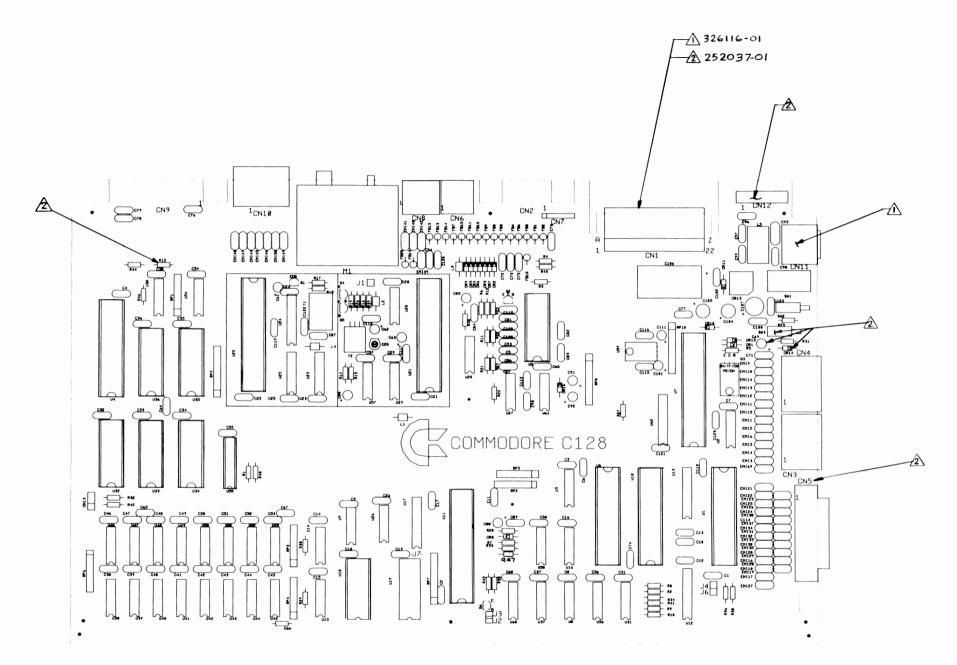

| PCB                                     |      |

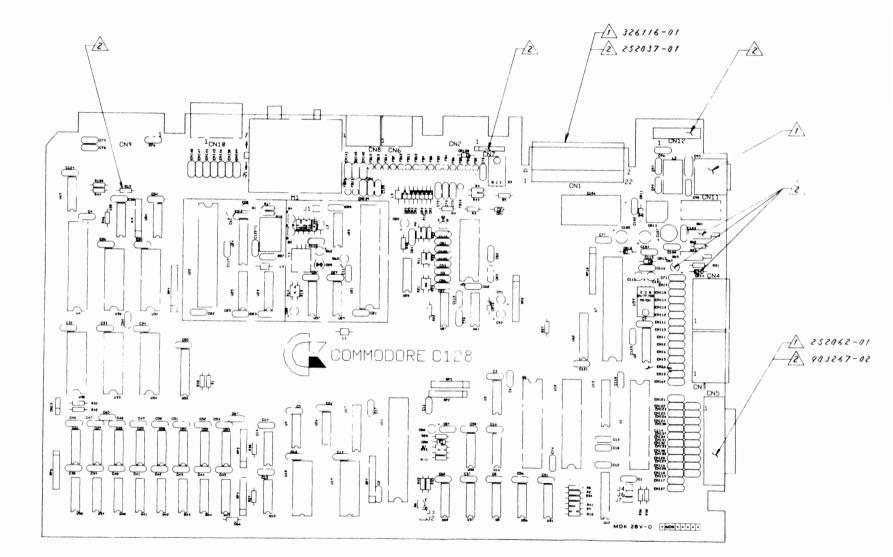

| PCB ASSEMBLY #310379 REV. 6             |      |

| BOARD LAYOUT                            | 54   |

| PARTS LIST                              | 55   |

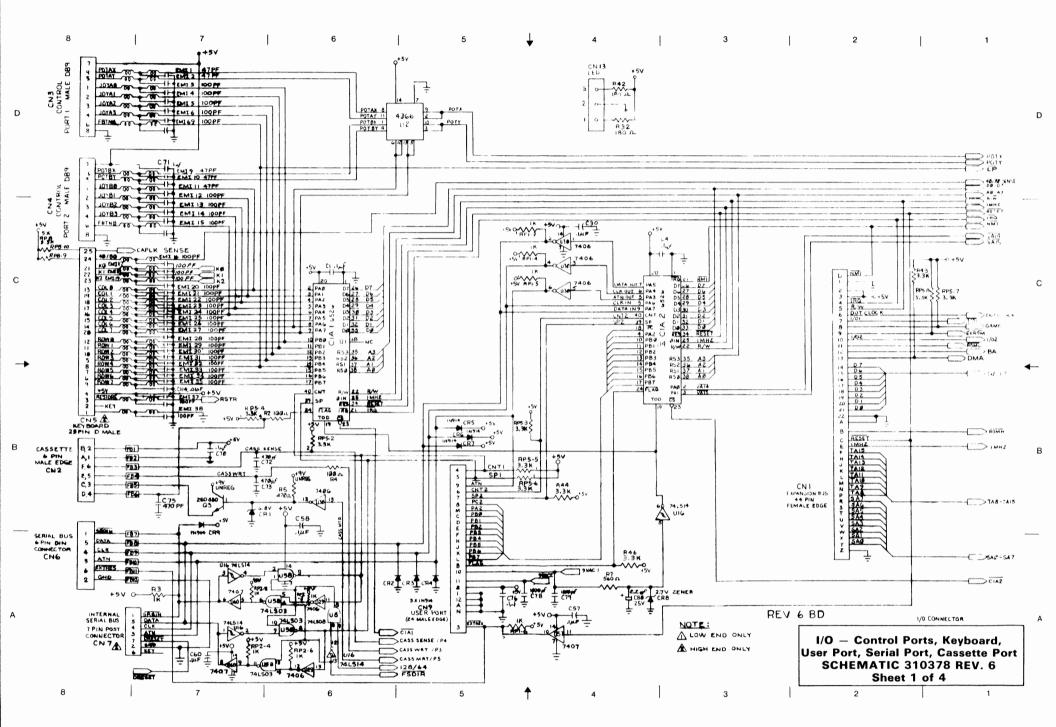

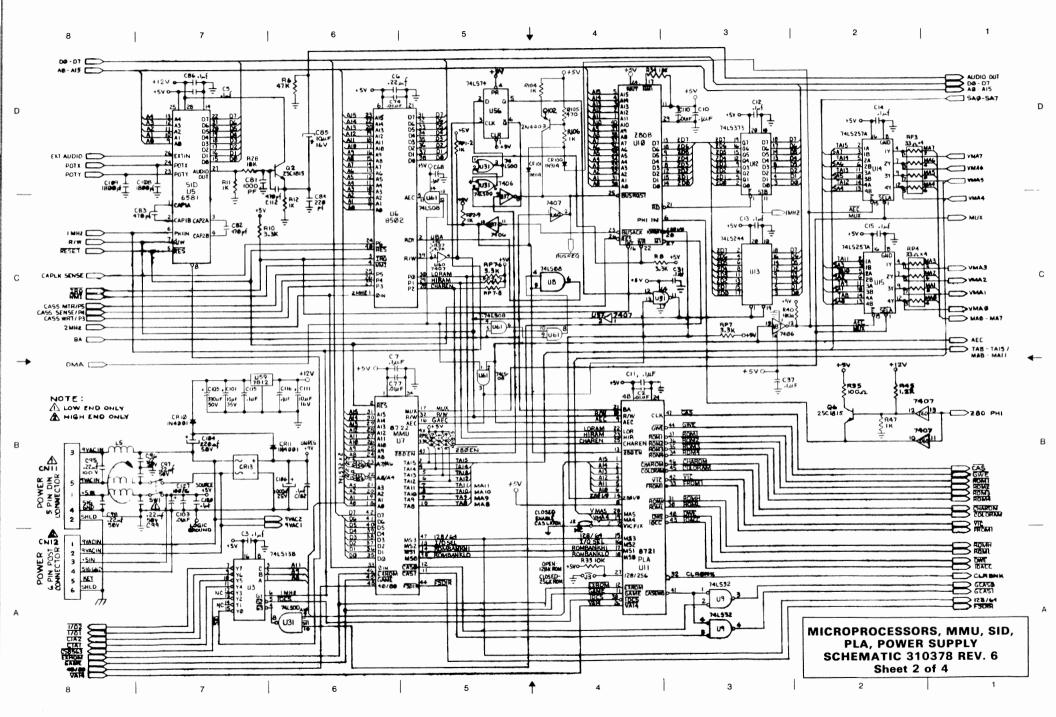

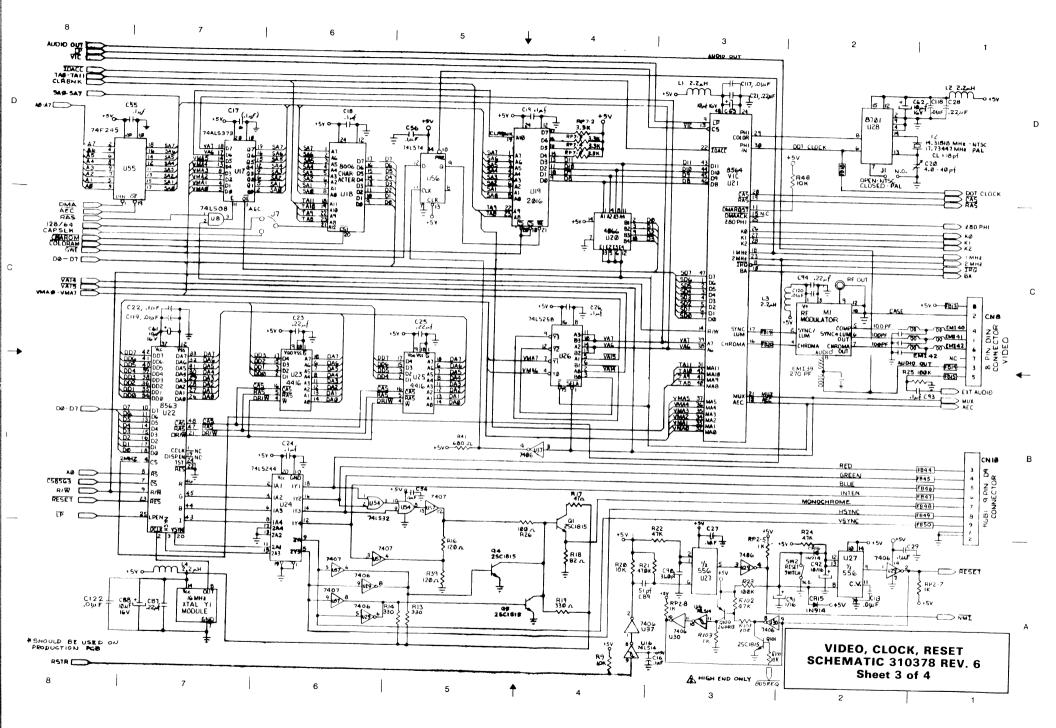

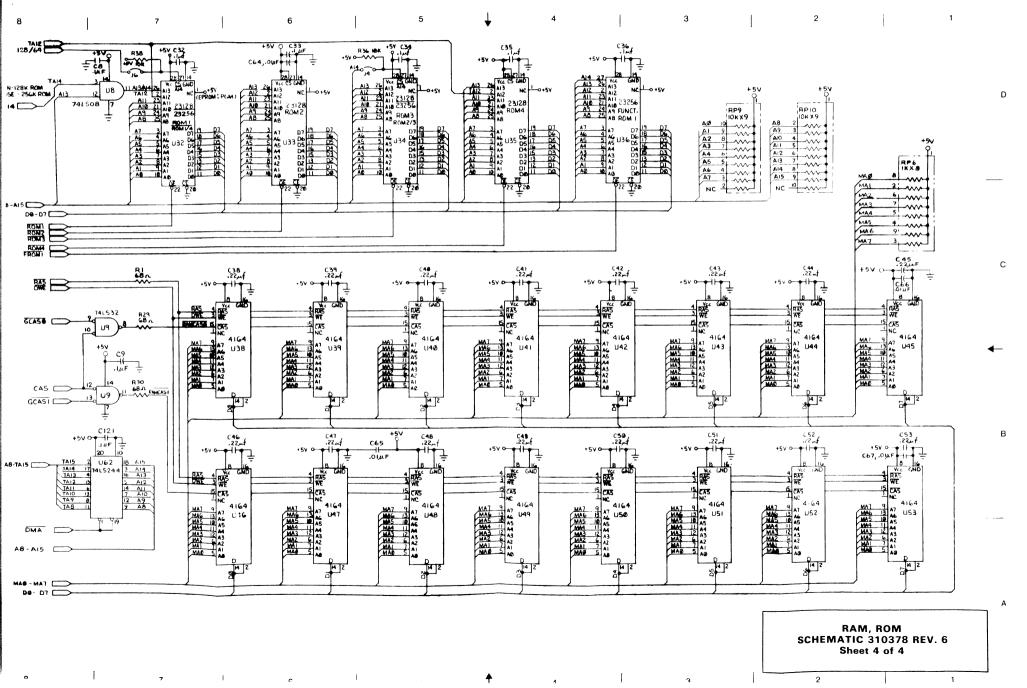

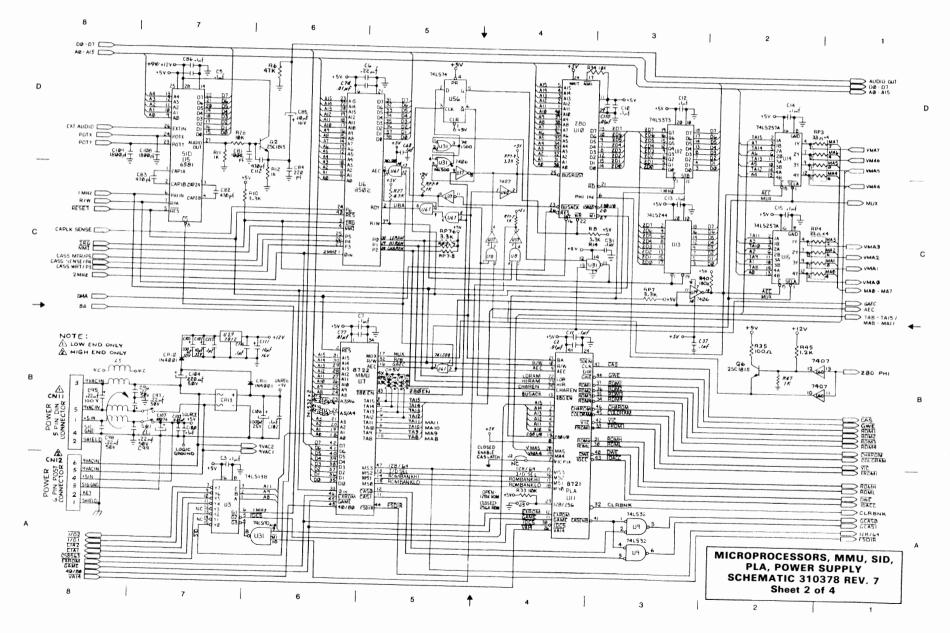

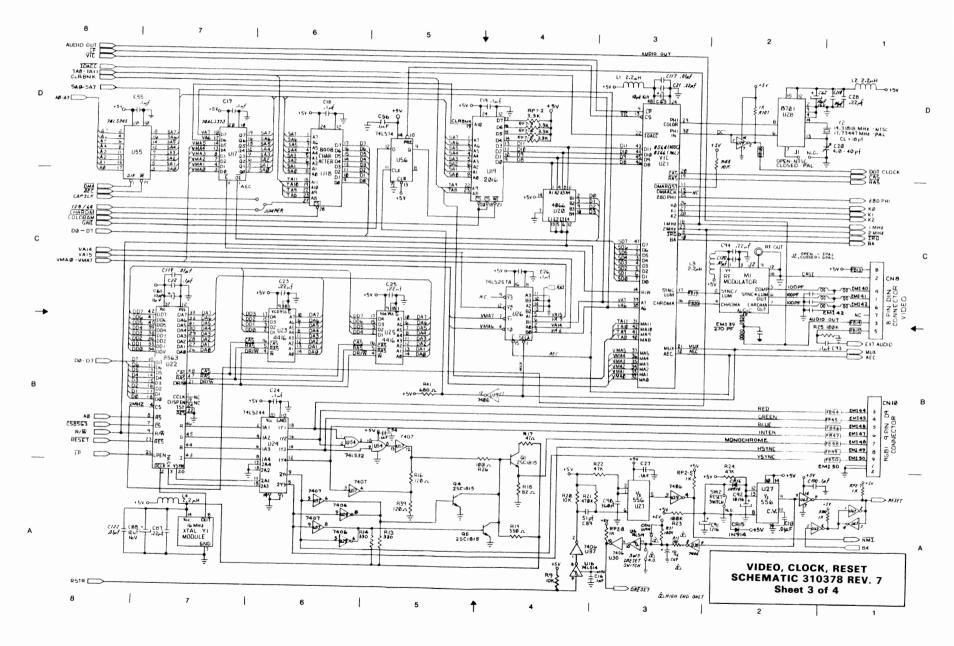

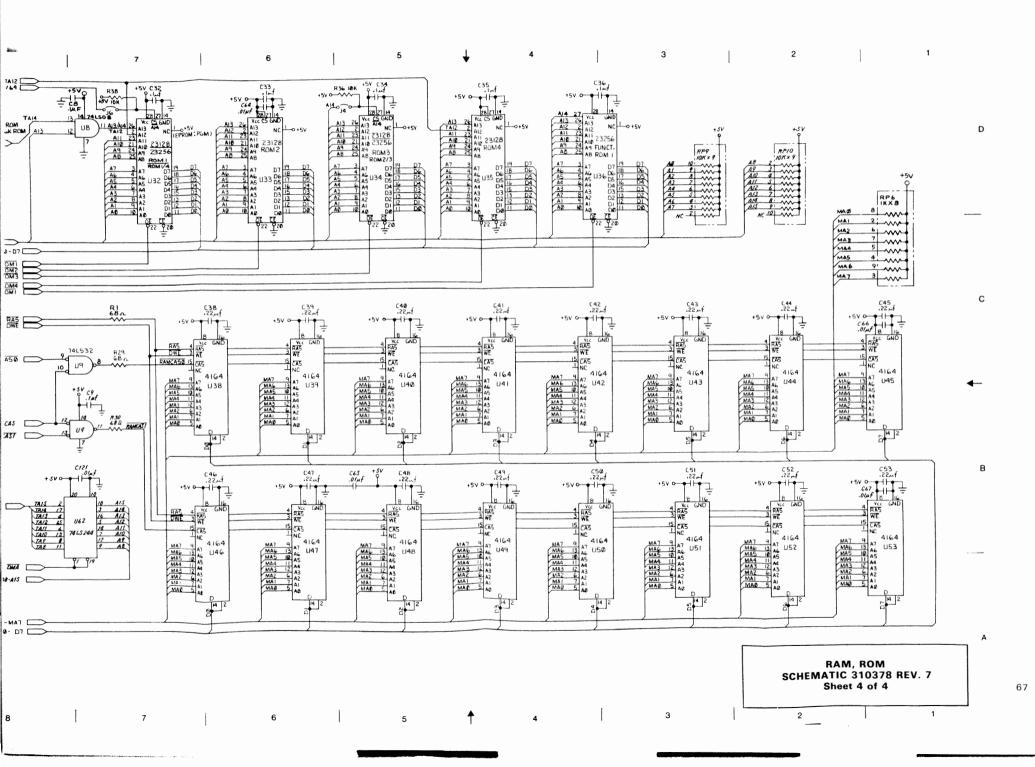

| SCHEMATIC DRAWINGS                      | 57   |

| PCB ASSEMBLY #310379 REV. 7             |      |

| BOARD LAYOUT                            | 61   |

| PARTS LIST                              | 62   |

| SCHEMATIC DRAWINGS                      | 64   |

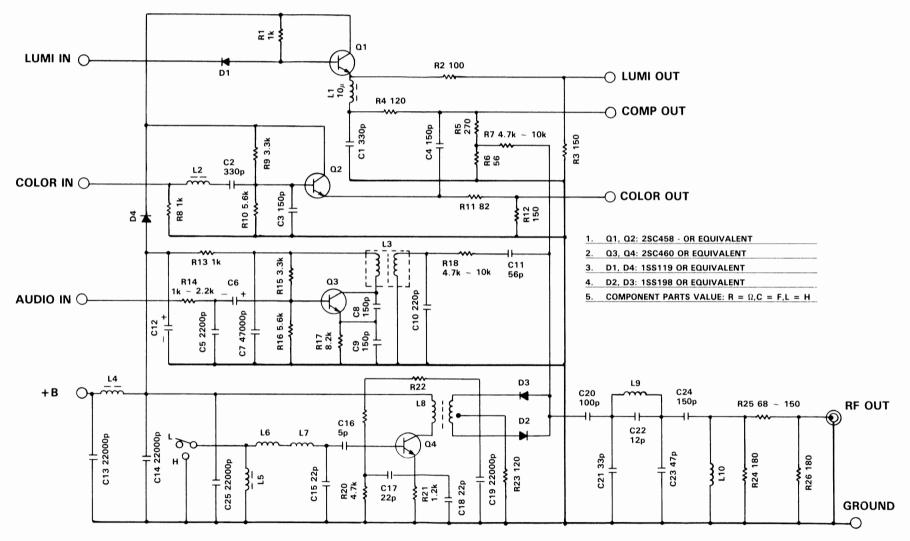

| RF MODULATOR NTSC                       | 68   |

#### e

# COMMODORE 128 | PERSONAL COMPUTER

| GENERAL FEATURES           | <ul> <li>Advanced Styling • 100% Compatible with Commodore 64</li> <li>Built-in, Easy to Use DOS support • RAM Expandable up to 512K RAM Using RAM Disk Option • Upper and Lower Case Character Set</li> <li>Built-in BASIC • 3 Separate Modes of Operation</li> </ul>                                                                                           |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64 MODE                    | <ul> <li>8502 Microprocessor (6502/6510 Compatible)</li> <li>6581 Sound<br/>Interface Chip</li> <li>64K RAM</li> <li>16K ROM</li> <li>BASIC 2.0</li> <li>40 x 25<br/>Lines (320 x 200 resolution)</li> <li>16 Colors</li> <li>8 Sprites</li> </ul>                                                                                                               |

| 128 MODE                   | <ul> <li>8502 Microprocessor (6502/6510 Compatible)</li> <li>6581 Sound Interface Chip • 128K RAM (Expandable to 512K Using RAM Disk Option) • 48K ROM + 16K ROM for DOS Support</li> <li>BASIC 7.0 • Machine Language Monitor • 40 x 25 Lines (320 x 200 resolution) • 80 x 25 Lines (640 x 200 resolution) • 16 Colors + 8 Sprites (40 Column Only)</li> </ul> |

| CP/M MODE                  | <ul> <li>Z80 Microprocessor • CP/M<sup>™</sup> Plus Version 3.0</li> <li>128K RAM (Expandable to 512K Using RAM Disk Option)</li> <li>40 x 25 Lines (320 x 200 resolution) • 80 x 25 Lines (640 x 200 resolution) • 16 Colors</li> </ul>                                                                                                                         |

| KEYBOARD                   | <ul> <li>Full Size Typewriter Style</li> <li>92 Keys</li> <li>14 Key Numeric Keypad</li> <li>8 Programmable Function Keys</li> <li>6 Cursor Keys</li> <li>Help Key</li> <li>40/80 Column Key</li> <li>No Scroll</li> <li>Line Feed</li> <li>Escape</li> <li>Tab</li> <li>Cap Lock</li> <li>Alt (Not all accessible in 64 Mode)</li> </ul>                        |

| INPUTS/OUTPUTS             | <ul> <li>User Port</li> <li>Cassette Port</li> <li>RF/TV Port</li> <li>Audio Input</li> <li>Composite Video</li> <li>Serial Port</li> <li>2 Game Ports</li> <li>Cartridge Port</li> <li>Audio Output</li> <li>Digital RGBI Video</li> </ul>                                                                                                                      |

| RECOMMENDED<br>PERIPHERALS | <ul> <li>MPS 802, MPS 803, MPS 1000 Printers</li> <li>1541, 1571 Single Disk Drive</li> <li>1901 Monochrome Monitor • 1902 Digital RGBI Color Monitor</li> <li>1660 and 1670 Modems • Fully Compatible with Commodore 64<br/>Software and Accessories in 64 Mode</li> </ul>                                                                                      |

| POWER REQUIREMENTS         | • 117 Volts AC, 60 Hz, 15 Watts                                                                                                                                                                                                                                                                                                                                  |

|                            | †Specifications subject to change without notice<br>*CP/M is a registered trademark of Digital Research, Inc.                                                                                                                                                                                                                                                    |

# PARTS LIST C-128

PLEASE NOTE: Commodore part numbers are provided for reference only and do not indicate the availability of parts from Commodore. Industry standard parts (Resistors, Capacitors, Connectors) should be secured locally. Approved cross-references for TTL chips, Transistors, etc. are available in manual form through the Service Department. Unique or non-standard parts will be stocked by Commodore and are indicated on the parts list by a "C".

# **TOP CASE ASSY**

| Top Case        | C 251987-01 |

|-----------------|-------------|

| Keyboard        | C 310401-01 |

| Nameplate       | C 310400-01 |

| Lamp Holder Set | C 252013-01 |

| LED Assembly    | C 250754-01 |

|                 |             |

# **BOTTOM CASE ASSY**

| Bottom Case          | С | 251988-01 |

|----------------------|---|-----------|

| Foot, Self-Adhesive  | С | 251993-01 |

| PCB Top Shield       | С | 252015-01 |

| PCB Bottom Shield    | С | 252016-01 |

| PCB Insulation Sheet | С | 252017-01 |

#### ACCESSORIES

| Users Manuals      |   |           |

|--------------------|---|-----------|

| Introductory Guide | С | 319773-01 |

| System Guide       |   | 310638-01 |

| Power Supply       | С | 310416-01 |

| RF Cable           | С | 326189-01 |

| Switch Box         | С | 904778-01 |

| Tutorial Diskette  | С | 317667-01 |

| CP/M Diskette #1   | С | 317430-01 |

| CP/M Diskette #2   | С | 317431-01 |

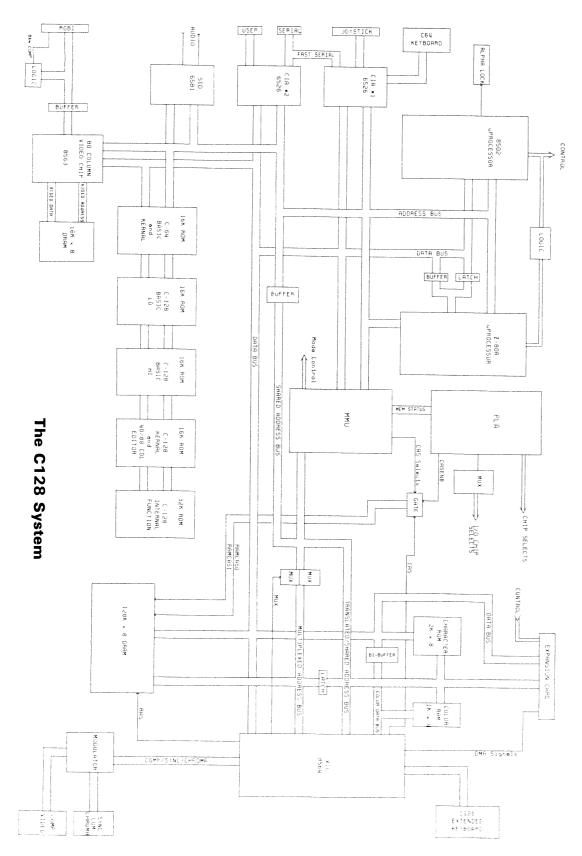

# **BLOCK DIAGRAN**

# **BUS ARCHITECTURE**

#### FOLD OUT SCHEMATIC PAGES 64-67 FOR EASY REFERENCE.

#### **The Processor Bus**

The **Processor Bus** is the data and address buses that are directly connected to the 8502 processor. These buses are designated  $D_0 - D_7$  for the eight bit data bus and  $A_0 - A_{15}$  for the sixteen bit address bus. These buses tie the processor to most of the system ROM and I/O devices, including at least part of all System ROM, all built-in Function ROM, the MMU, the PLA, the 8563 Video Processor, the SID, and both CIA chips.

The Processor Bus is in direct communication with the Z-80 co-processor as well. All address lines are shared directly by both processors. In order to allow the Z-80 to operate on a 6502 family bus, it is necessary to latch data going into the Z-80 and gate the data leaving the Z-80. Thus, the Z-80 has a small local data bus, designated ZD<sub>0</sub>-ZD<sub>7</sub>. During a write cycle, when AEC is high, Z-80 data is gated to the Processor Bus. During a read cycle, Processor Bus data is gated to the Z-80 data bus. This read data is transparently latched by the 1 MHz system clock.

The read and write cycles referred to are, unless otherwise specified, 8502 type bus cycles. The Z-80 Read Enable and Write Enable outputs are conditioned using logic to interface with an 8502 bus cycle, so no distinction is made as to the differences between cycles of the different processors.

As mentioned above, the Z-80 is not in direct communication with the Processor Data Bus, due to the necessity of adapting the Z-80 to 8502 bus protocol. Note, however, that every other device and the translated bus (except two that will be explained later) shares the Processor Data Bus as a common data bus.

#### The Translated Address Bus

Another C128 system bus is the **Translated Address Bus**, which is produced by the MMU during AEC high. This bus consists of only high order addressing lines, designated TA<sub>8</sub> - TA<sub>15</sub>. These lines reflect the action of the MMU on the normal high order address lines, which may or may not include some sort of translation. The MMU can translate the address of page zero or page one in normal operation, and it translates the Z-80 address from \$0000 thru \$0FFF in order to direct it to read the Z-80 BIOS. A more complete description of MMU translations can be found in the MMU section. Normally the Translated Address Bus indirectly drives the DRAMs and the VIC chip by driving the Multiplexed Address Buses. It directly drives System ROM 4 address line 12 to allow the Z-80 ROM relocation. Finally, this bus becomes address lines 8 thru 15 of the C64 compatible expansion port.

During a VIC cycle or a DMA, the MMU pulls  $TA_{12} - TA_{15}$  high, while  $TA_8 - TA_{11}$  are tri-stated. This allows the VIC chip to drive  $TA_8 - TA_{11}$  as VIC addresses  $VA_8 - VA_{11}$ .

#### The Multiplexed Address Bus

This section actually describes two related address buses, the **Multiplexed Address Bus** and the **VIC Multiplexed Address Bus**, known respectively as  $MA_0 - MA_7$  and  $VMA_0 - VMA_7$ . The VIC Multiplexed Address Bus is created during AEC high by multiplexing the high order Translated Address Bus (TA<sub>8</sub> - TA<sub>15</sub>) with the low order Processor Address Bus (A<sub>0</sub> - A<sub>7</sub>), controlled via the MUX signal. This bus, driven though series resistors, is called the Multiplexed Address bus. The VIC Multiplexed Address Bus is used in addressing the VIC chip registers while the Multiplexed Address Bus is the processor's DRAM address for both 64K banks of DRAM.

#### **BUS ARCHITECTURE (Continued)**

During a VIC cycle, AEC low, the VIC chip address lines must be asserted. There is no completely separate address bus for the VIC addresses, so it shares the VMA<sub>0</sub> - VMA<sub>7</sub> and TA<sub>8</sub> - TA<sub>11</sub> address lines that are otherwise tri-stated during AEC low. Most of the VIC addresses come out of the VIC chip already multiplexed, but two of them, VA<sub>6</sub> and VA<sub>7</sub>. They do not supply column information, as the VIC chip supplies only fourteen bits of addressing. The higher order address bits VA<sub>14</sub> and VA<sub>15</sub> come from CIA 2, as in the C64. Thus, the VIC supplies complete VMA<sub>0</sub> - VMA<sub>7</sub> for a VIC DRAM access or DRAM refresh. The TA<sub>8</sub> - TA<sub>11</sub> supplied by VIC are used in conjunction with another addressing bus for non-multiplexed VIC cycle addresses, such as Character ROM and Color RAM accesses.

#### **The Shared Address Bus**

The **Shared Address Bus** is a non-multiplexed address bus used by both the processor and the VIC chip. This is necessary to communicate with common resources, namely the Character ROM and Color RAM. During AEC high, the Shared Address Bus, designated  $SA_0 - SA_7$ , is driven by  $A_0 - A_7$ , the lower order Processor Address bits. The higher order bits needed are supplied by the Translated Address Bus, which is also a shared address bus. Thus, the processor is able to access both shared items.

During AEC low, the VIC addresses  $VA_0 - VA_7$  (VMA<sub>0</sub> - VMA<sub>7</sub>) must come onto the Shared Address Bus. Since  $VA_0 - VA_6$  are actually multiplexed, the row address only must be sent to the Shared Address Bus. Thus, the Multiplexed VIC addresses are transparently gated when either RAS or MUX are low, but latched when both are high, which would indicate that a column address is about to be presented. The high order address bits, as well, are supplied by the shared Translated Address Bus. Note that the Shared Address Bus provides the lower eight bits of the expansion port address, allowing VIC access to cartridges and some additional drive capability by way of the TTL chips used to drive the Shared Address Bus.

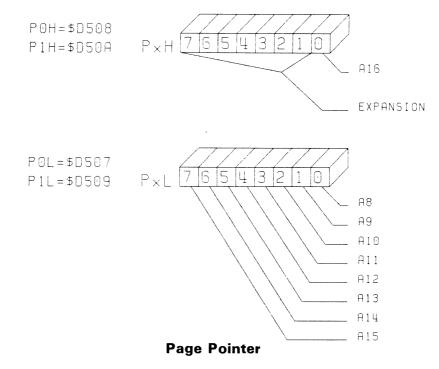

#### The Color Data Bus

The Color RAM is written to or read from by a nybble data bus called the **Color Data Bus**. During AEC high, the Color Data Bus is connected to the lower half of the Processor Data Bus via an analog switch, allowing the Processor full access to the Color RAM. During AEC low, that switch is opened, effectively isolating the Color Data Bus from the Processor Data Bus. In this state, it is driven by the VIC extended data bus D<sub>8</sub> - D<sub>11</sub>.

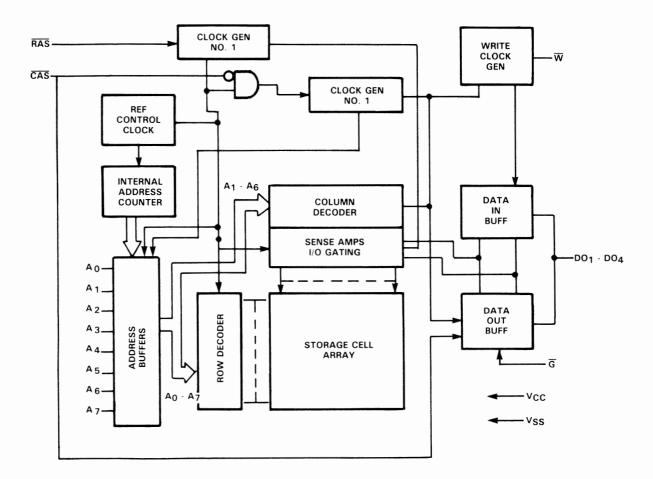

#### The Display Bus

The Display Bus is a bus local to the 8563 Video Controller VIC chip, consisting of the **Display Address**, DA<sub>0</sub> - DA<sub>7</sub>, and the **Bus Display Data Bus**, DD<sub>0</sub> - DD<sub>7</sub>. This local bus supports the 8563 display RAM, which is completely isolated from the rest of the C128 system. The Display Address Bus is a multiplexed address bus providing addressing to the display DRAM. The Display Data Bus provides communication between this DRAM and the 8563. The 8563 also provides row and column strobes and dynamic refresh to this DRAM.

# FOLD OUT SCHEMATIC SHEET 2, PAGE 65, FOR EASY REFERENCE.

The 8502 is an HMOSII Technology microprocessor similar to the 6510/6502. It is the normal operating processor and is used in the C64 and the C128 modes. Fully software compatible with the 6510, hence the 6502, the 8502 also features a zero page port used in memory management and cassette implementations. The 8502 is also specified for operation at 2 MHz. The 2 MHz operation is made possible by removing the VIC from the system. The VIC chip is never completely removed from the C128 system, as it continues to function as clock generator and bus arbitrator. However, the VIC is removed as a display chip and co-processor, thus the full clock cycle can be devoted to processor functioning instead of sharing the cycle with the VIC. The task of video display processor is then taken over by the 8563, which can function without the need for bus sharing that the VIC required. Since the I/O devices, SID, etc., are rated at 1 MHz only, stretching of the 2 MHz clock is used to allow these parts to be directly accessed by the 2 MHz operation as they are still driven by a 1 MHz source (and as such, all timer operations remain unchanged), and clock stretching is only used to synchronize the 2 MHz machine cycle to the 1 MHz  $\phi_0$  high time. The clock sources and clock stretching capabilities are generated by the VIC chip.

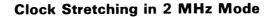

#### **CLOCK STRETCHING**

When running in 2 MHz mode, the processor clock sometimes must be stretched. This is handled by the VIC chip, the processor, and the PLA working together. When an I/O operation is decoded during a 2 MHz cycle, the phase relationship between the 2 MHz and the 1 MHz clocks must be considered. If the 2 MHz access occurs during 1 MHz  $\phi_1$ , the access to a clocked I/O chip would be out of synchronization with the 1 MHz clock that drives all I/O chips. Thus, during this phase relationship, IOACC, from the PLA, signals the VIC chip to extend the 2 MHz clock. Should the 2 MHz cycles take place during the 1 MHz  $\phi_2$  cycle, no special attention is necessary.

Please take note to consider the speed implications of this. In 2 MHz mode, half of the I/O accesses given will occur at an effective speed of 1 MHz. For time critical operations, then, accesses to I/O chips are kept at a minimum.

# THE 8502 MICROPROCESSOR (Continued)

|                  |                                                                            |                                                                                                                | 1              | ØO                   | Phase O clock input. This is the dual speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5020<br>'ROC     | ESS                                                                        | SOR                                                                                                            | 2<br>3         | RDY                  | system clock for the 128.<br>Ready. TTL level input, used to DMA the<br>8502. The processor operates normally while<br>RDY is high. When RDY makes a transition to<br>the low state, the processor will finish the<br>operation it is on, and any subsequent opera-<br>tion if it is a write cycle. On the next occur-<br>rence of read cycle the processor will halt,<br>making it possible to tri-state the processor<br>to gain complete access to the system bus.<br>The Interrupt Request input is a request that<br>the processor will complete execution of the<br>current instruction before recognizing the re-                                                                                                                                                                                                                                                                       |

| 02<br>80-<br>SOR | 40<br>39<br>38<br>37<br>36<br>35<br>34<br>32<br>31<br>30<br>29<br>28<br>27 | - RES<br>- R/W<br>- D0<br>- D1<br>- D2<br>- D3<br>- D4<br>- D5<br>- D6<br>- D7<br>- P0<br>- P1<br>- P2<br>- P3 | 4              | NMI                  | quest. At that time, the interrupt mask in the<br>Status Code Register will be examined. If the<br>interrupt mask is not set, the processor will<br>begin an interrupt sequence. The Program<br>Counter and the Processor status register will<br>be stored on the stack and the interrupt<br>disable flag is set so that no other interrupts<br>can occur. The processor will then load the<br>program counter from the memory location<br>\$FFFE and \$FFFF.<br>The Non-Maskable Interrupt Request is a<br>negative-edge sensitive request that the pro-<br>cessor initiate an interrupt sequence. The pro-<br>cessor will complete execution of the current<br>instruction before recognizing the request.<br>The Program Counter and the processor<br>status register will be stored on the stack.<br>The processor will then load the program<br>counter from the memory locations \$FFFA |

|                  | 27<br>26<br>25<br>24<br>23<br>22<br>21                                     |                                                                                                                | 5<br>6<br>7-20 | AEC<br>VDD<br>A0-A15 | and \$FFFB.<br>The Address Enable Control. The Address<br>Bus is only valid when the AEC line is high.<br>When low, the address bus is in a high<br>impedance state. This allows DMA's for dual<br>processor systems.<br>5VDC input.<br>Address bus outputs. Unidirectional bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | 21                                                                         | - 033                                                                                                          | 22,23          |                      | used to address memory and I/O devices. The address bus can be disabled by controlling the AEC input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                  |                                                                            |                                                                                                                | 21<br>24-30    | VSS<br>PO-P6         | DC ground.<br>Bidirectional I/O port used for transferring<br>data to and from the processor directly. The<br>Data Register is located at location \$0001<br>and the Data Direction Register is located at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  |                                                                            |                                                                                                                | 31-38          | D0-D7                | location \$0000.<br>Bi-directional bus for transferring data to and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  |                                                                            |                                                                                                                | 39             | R/W                  | from the device and the peripherals.<br>The read/write line is a TTL level output from<br>the processor to control the direction of data<br>transfer between the processor and memory,<br>peripherals, etc. This line is high for reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  |                                                                            |                                                                                                                | 40             | RES                  | memory and low for writing.<br>The Reset input is used to reset or start the $\mu$ processor from a power down condition.<br>During the time that this line is held low,<br>writing to or from the $\mu$ processor is inhibited.<br>When a positive edge is detected on the in-<br>put, the $\mu$ processor will immediately begin<br>the reset sequence. After a system initializa-<br>tion time of 6 cycles, the mask interrupt flag<br>will be set and the processor will load the<br>program counter from the contents of the<br>memory locations \$FFFC and \$FFFD. This is<br>the start location for program control. After<br>V <sub>CC</sub> reaches 4.75 volts in a power up<br>routine, reset must be held low for at least 2<br>cycles. At this time the R/W line will become<br>valid.                                                                                             |

# 315020 8502 MICROPROCESSOF

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | NMI<br>AEC<br>VDD<br>A0<br>A1<br>A2<br>A3<br>A3<br>A3<br>A3<br>A3<br>A3<br>A5<br>A5<br>A5<br>A5<br>A5<br>A5<br>A10<br>A10<br>A11<br>A12 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | $\mu$ PRO- | 37<br>36<br>35<br>34<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>23<br>22 | - D1<br>- D2<br>- D3<br>- D4<br>- D5<br>- D6<br>- D7<br>- P0<br>- P1<br>- P2<br>- P3<br>- P4<br>- P5 |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

# FOLD OUT SCHEMATIC SHEET 2, PAGE 65, FOR EASY REFERENCE.

The Z-80 microprocessor is used as a secondary processor in the C128 to run CP/M based programs. The Z-80 is interfaced to the 8502 bus and can access all of the devices that the 8502 can access.

#### **Bus Interface**

Since a Z-80 bus cycle is much different than a 65xx family bus cycle, a certain amount of interfacing is required for a Z-80 to control a 65xx type bus. Since the Z-80 has built-in bus arbitration control lines, it is possible to isolate the Z-80 by tri-stating its address line. Thus, the Z-80 and 8502 both share common address lines.

The data lines do not interface quite as easily. Due to the shared nature of the bus during Z-80 mode, it is necessary to isolate the Z-80 from the bus during AEC low. Thus, a tri-stable buffer must drive the Processor bus during Z-80 data writes. The reverse problem occurs during a Z-80 read — the Z-80 must not read things that are going on during AEC low. It must latch the data that was present during AEC high. Thus, a transparent latch drives the data input to the Z-80. It is gated by the Z-80 Read Enable output, and latched when the 1 MHz clock is low. It will be seen that the Z-80 actually runs during AEC low, but that the data bus interfaces with it only during AEC high.

#### **Control Interface**

The Z-80 control interfacing must provide useful clock pulses to the Z-80 and must tailor the Z-80 Read and Write Enable signals for the 8502 type bus protocol. The Z-80 clock is provided by the VIC chip, and is basically a 4 MHz clock that only occurs during  $\phi_0$  low, as seen in the Z-80 bus timing diagram. This insures that the Z-80 is only clocked when it is actively on the bus. One additional problem that arises in clocking the Z-80 is that while all of the 8502 levels, and most of the Z-80 levels, are TTL compatible, the Z-80 clock input expects levels very close to five volts. For that reason, the ouptut from the VIC chip is processed by a transistor switching circuit to give a full amplitude clock. This circuit uses the nine volt supply, thus, the nine volt circuit **must** be operational for the Z-80 to function.

**Z-80 Bus Timing**

#### THE Z-80 MICROPROCESSOR (Continued)

The Z-80 is designed to have explicit Read, Write and I/O cycles, where an I/O cycle is distinct from a memory cycle. The 65xx family uses only memory mapped I/O and thus, for a 65xx bus, all I/O devices appear as memory locations, and all non-write cycles appear as read cycles. The Z-80 communicates cycle information via two control lines, the Read Enable and Write Enable lines. The C128 uses the Read Enable line of the Z-80 to gate the Processor Bus data to the Z-80 data bus. The Write Enable interfacing is somewhat more complicated.

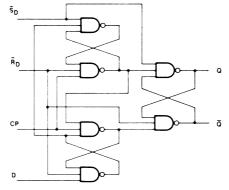

The Write Enable Circuitry consists of a rising-edge triggered D-Type flip-flop and an SR flip-flop. The D-flop is triggered by the rising-edge of the 1 MHz clock. The positive output of the SR drives the D-input, and the Q output gated with AEC drives an open collector inverter, which in turn drives the R/W line of the 8502 bus. The S input is driven by the Z-80 WE, and the R input is driven by the Q output of the D-flop. Normally the D-input is low, resulting in an 8502 read cycle. When the Z-80 WE signal falls, it sets the SR flop, causing the D-input to rise. This line remains high, even if the Z-80 WE should rise again. When the 1 MHz clock rises, this high level is clocked, causing an 8502 write cycle that will last one complete 1 MHz cycle. When the Write signal is passed by the D-flop, the Q output will reset the SR flop. If no more WE signals come, the D-flop will once again set 8502 Read mode.

#### **Processor Switching**

It is important in normal operation for the Z-80 and 8502 to operate as co-processors, communicating between each other. This is, however, only serial co-processing, not to be considered parallel co-processing or multiprocessing. Only one processor may have the bus at any one time. This is important in several ways. First, the C128 system must power up with the Z-80 as the master processor. This is because the Z-80 will not power up cleanly, and may accidently access the bus when powering up. Thus, it is made master on powerup and can do anything it likes to the bus. Also, the Z-80 can start up certain C64 applications that would cause the 8502 to crash, thus again it is the logical choice for startup processor. After some initializations, the Z-80 will start up the 8502 in either C128 or C64 mode, depending upon if a cartridge is present.

The second reason for processor switching is to allow the Z-80 to access 8502 Kernal routines. For standardized programs, or for any I/O operation not supported in the Z-80 BIOS, the Z-80 can pass on the task of I/O to the 8502. Since the Z-80 sees BIOS ROM where the 8502 sees its pages 0 through F, the Z-80 can operate without fear of disrupting any 8502 pointers or the stack in RAM Bank 0.

The Z-80 can receive a bus grant request from the MMU, via Z80EN, or from the VIC chip, via BA. Since the VIC control line is used for DMAs, that is not of immediate concern. The Z80EN action, however, is, since it is the mechanism by which processors swap control. When the Z80EN line goes high, it triggers a Z-80 BUSRQ. The Z-80 will relinquish the bus by pulling BUSACK low. This action drives the 8502 AEC high and, providing VIC does not request a DMA, will also drive the 8502 RDY line high, enabling the 8502. To switch back, a low on the Z-80 BUSRQ will result in Z-80 BUSACK going high, tri-stating and halting the 8502.

# 906150 Z-80 MICROPROCESSOR

| A11-     | 1  |            | 40 | -A10              |

|----------|----|------------|----|-------------------|

| A12-     | 2  |            | 39 | -A9               |

| A13-     | 3  |            | 38 | -A8               |

| A14-     | 4  |            | 37 | -A7               |

| A15-     | 5  |            | 36 | —A6               |

| PHI-     | 6  |            | 35 | -A5               |

| D4-      | 7  |            | 34 | -A4               |

| D3-      | 8  |            | 33 | -A3               |

| D5-      | 9  |            | 32 | -A2               |

| D6-      | 10 | Z-80       | 31 | -A1               |

| VCC-     | 11 | $\mu$ Pro- | 30 | -A0               |

| D2-      | 12 | cessor     | 29 | - <u>VSS</u>      |

| D7-      | 13 |            | 28 | -RFSH             |

| DO-      | 14 |            | 27 | $-\underline{M1}$ |

| <u></u>  | 15 |            | 26 | -RESET            |

|          | 16 |            | 25 | -BUSRQ            |

|          | 17 |            | 24 | -WAIT             |

| HALT-    | 18 |            | 23 | -BUSAK            |

| MEMREO - | 19 |            | 22 | $-\overline{WR}$  |

|          | 20 |            | 21 | -RD               |

| 1-5,<br>30-40       | A0-A15       | 16 Bit tri-stating Address Bus. Used for<br>16 bit memory address during memory<br>cycles, used for 8 bit I/O address during I/O<br>cycles. This allows up to 256 input or 256<br>output ports. During refresh time, the lower 7<br>bits contain a valid refresh address.                                                                                                                                                                                                                                             |

|---------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>7-10,<br>12-15 | PHI<br>D0-D7 | Single phase system clock.<br>Input/Output Data Bus, capable of tri-stating,<br>used for 8-bit data exchanges with memory<br>and I/O devices.                                                                                                                                                                                                                                                                                                                                                                         |

| 11<br>16            | VCC<br>INT   | SVDC input.<br>Interrupt Request. Active low input, driven by<br>external devices. If the interrupt flag IFF is<br>enabled, and the BUSRQ line is not active,<br>the processor will honor the requested inter-<br>rupt at the end of the current instruction.<br>When the Z-80 acknowledges an interrupt, it<br>generates an interrupt acknowledge signal<br>(IORQ during M <sub>1</sub> ) at the beginning of the<br>next instruction cycle. There are three<br>different modes of response to a given<br>interrupt. |

| 17                  | NMI          | Non-Maskable Interrupt. Active low input.<br>This interrupt is edge triggered and cannot be<br>masked against. It is always recognized at<br>the end of the current instruction, forcing the<br>Z-80 to take a restart at location \$0066. The<br>program counter is automatically saved in the<br>stack to allow a return from the interrupted<br>program. Note that continuous WAIT cycles<br>can delay an NMI by preventing the end of<br>the current cycle, and that BUSRQ will over-<br>ride NMI.                |

| 18 | HALT   | Halt State. Active low output indicating that<br>the Z-80 has executed a HALT instruction<br>and is awaiting some kind of interrup <u>t before</u><br>execution can continue. While in the HALT<br>state, the CPU continuously executes NOPs                                                                                                                                                                                                                                                   |

|----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | MEMREQ | to continue refresh activity.<br>Memory Request. Active low, tri-state output<br>that indicates that the address bus holds a<br>valid address for a memory read or write                                                                                                                                                                                                                                                                                                                       |

| 20 | IORQ   | operation.<br>Input/Output Request. Active low, tri-state<br>output. The IORQ signal indicates that the<br>lower half of the address bus holds a valid<br>address for an I/O read or write operation. An<br>IORQ signal is also generated with an $M_1$<br>signal when an interrupt is being acknowl-<br>edged to indicate that an interrupt response<br>vector can be placed on the data bus. An<br>interrupt can be acknowledged during $M_1$ :<br>I/O operations never occur during $M_1$ . |

| 21 | RD     | Memory Read. Active low, tri-state output.<br>RD indicates that the CPU wants to read data<br>from memory or from an I/O device. This<br>signal is generally used to gate read data                                                                                                                                                                                                                                                                                                            |

| 22 | WR     | onto the data bus.<br>Memory Write. Active low, tri-state output.<br>WR indicates that the data bus holds valid<br>data to be processed by memory or by an I/O<br>device.                                                                                                                                                                                                                                                                                                                      |

| 23 | BUSAK  | Bus Acknowledge. Active low output, used<br>to indicate to any device taking over the bus<br>that the Z-80 has gone into tri-state and the<br>bus has been granted. While in this mode it<br>cannot refresh dynamic memory.                                                                                                                                                                                                                                                                    |

| 24 | WAIT   | Wait. Active low input, used to drive the Z-80 into wait states. As long as this signal is low, the Z-80 will execute wait states, allowing this signal to be used to access slow memory and 1/0 devices. While the Z-80 is in a WAIT state, it cannot refresh                                                                                                                                                                                                                                 |

| 25 | BUSRQ  | dynamic memory.<br>Bus Request. Active low input that is used to<br>request the CPU address, data, tri-statable<br>output control signals to all go tri-state for<br>bus sharing and DMAs. The lines go tri-state<br>upon termination of the current machine                                                                                                                                                                                                                                   |

| 26 | RESET  | cycle.<br>Reset. Active low input which forces the pro-<br>gram counter to zero and initializes the Z-80,<br>which will set interrupt mode 0, disable inter-<br>rupts, and set registers I and R to zero.<br>During RESET, address and data buses tri-<br>tres and all adher signals on inactive                                                                                                                                                                                               |

| 27 | M1     | state and all other signals go inactive.<br>Machine Cycle One. Output, active low. This signal indicates that the current machine cycle is the OP code fetch of an instruction execution. During execution of a two byte op-code, $\overline{M_1}$ is generated as each byte is fetched. $\overline{M_1}$ also occurs with $\overline{\text{IORO}}$ to indicate an interrupt acknowledge cycle.                                                                                                |

| 28 | RFSH   | Refresh. Active low output used to indicate that the address bus holds a refresh address in its lower seven bits. Thus, the current $\overline{MREQ}$ signal should be used to do a refresh read to all dynamic memories not refreshed from an alternate source. A7 is set to zero and the upper eight bits contain the I register                                                                                                                                                             |

| 29 | VSS    | at this time.<br>Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **MEMORY ARCHITECTURE**

FOLD OUT SCHEMATIC PAGES 64-67 FOR EASY REFERENCE.

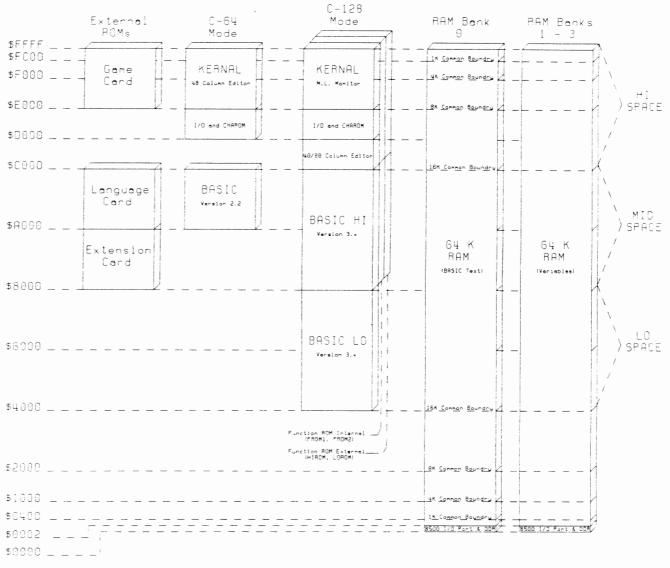

# **C128 ROM Memory Organization**

The memory map is an important consideration in maintaining C64 compatibility. The standard map is shown for the C64 mode. The C128 basically becomes a C64 when in C64 mode.

#### **MEMORY ARCHITECTURE (Continued)**

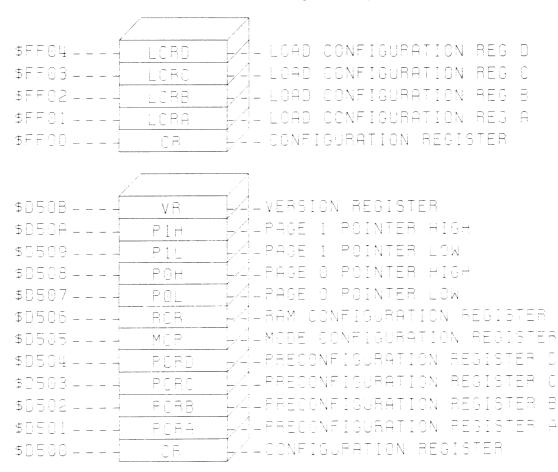

C128 mode is achieved at system reset, and is controlled by a bit in the MMU configuration register (See MMU Circuit Theory, page 20). In C128 mode, the MMU asserts itself in the C128 memory map at \$FF00 and in the I/O space starting at \$D500. Use of MMU registers, located at \$FF00, allows memory management without actually having the I/O block banked in at the time and with a minimum loss of contiguous RAM. The MMU is removed from the memory map in C64 mode but is still used by hardware to manage memory.

The ROMs in C64 mode, both internally and externally, look just like C64 ROMs. The internal BASIC and KERNAL provide the C64 mode with the normal C64 operating system in ROM. This ROM actually duplicates some of the ROM used in C128 mode, but is necessary, as it is not accessible from C128 mode. In C128 mode, up to 48K of Operating System is present, with the exact amount being set by software control. This allows quicker access to underlying RAM by turning off unneeded sections of the Operating System.

The External ROMs represented on the memory map are those used in the C64 mode, and obey the C64 rules for mapping, i.e., cartridges assert themselves in hardware via the EXROM and GAME lines. External ROMs in C128 mode are mapped as banked ROMs, such that when the system is initialized, all ROM slots are polled for the existance of a ROM and the ROM's priority if one exists. This allows much more flexibility than the hardwire ROM substitution method, since the Kernal and Basic ROMs can be swapped out for an application program, swapped out for external program control, or turned off all together. This banking manipulation is accomplished by writing to the Configuration Register at location \$D500 or \$FF00, in the MMU.

The hardware also features the ability to store preset values for the configuration and force a load of the Configuration Register by writing to one of the LCR (Load Configuration Register) registers.

#### **C128 RAM Memory Organization**

Refer again to the **C128 Memory Map**. The RAM present in the system is actually composed of two 64K by 8 bytes of contiguous DRAM. The RAM is accessed by selecting one of the two banks of 64K according to the RAM banking rules set in the RAM Configuration Register of the MMU. The area shown as RAM is representative of what the  $\mu$ Processor would see if all ROM were disabled. Bank switching can be accomplished in one of two ways.

The bank in use is a function of the value stored in the Configuration Register. A store to this register will always take effect immediately. An indirect store to this register, using preprogrammed bank configuration values, can be accomplished by writing to one of the **indirect load** registers, known as LCRs (Load Configuration Register), located in the \$FF00 region of memory. By writing to an LCR the contents of its corresponding PCR (PreConfiguration Register) will be latched into the configuration register. Refer to the MMU section on page 20 and the Alternate Memory Configurations on the following page.

When dealing with 64K banks of memory at once, it may be desirable to bank in bank 1 but still retain the system RAM (Stack, Zeropage, Screen, etc.). The MMU has provisions for what is referred to as common RAM. This is the RAM that does not bank, and is programmable in size and as to whether it appears at the top, bottom, or both in the memory map. The size is set by bits 0 and 1 in the RAM Configuration Register (RCR). If the value of the bits is zero, 1K will be common. Values of one, two, and three produce common areas of 4K, 8K, and 16K respectively. If bit 2 of the RCR is set, bottom memory is held common, if bit 3 is set, then top memory is common. In all cases, common RAM is physically located in bank 0.

# **MEMORY ARCHITECTURE (Continued)**

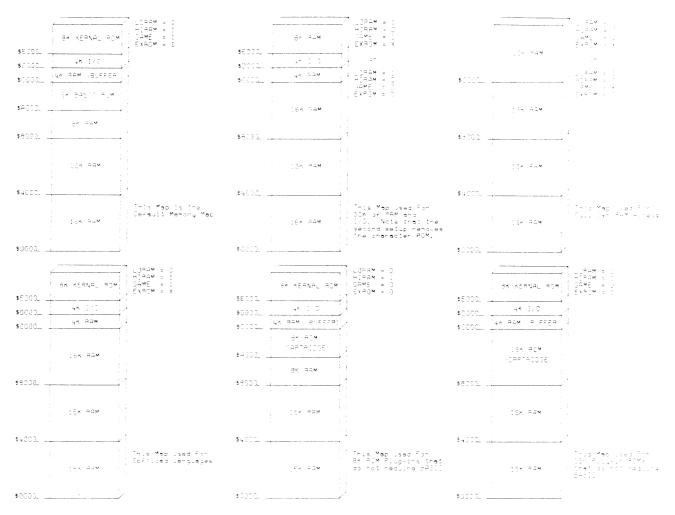

**C64** Alternate Memory Configurations

Zero page and page one can be located (or relocated) independently of the RCR. When the processor accesses an address that falls within zeropage or page one, the MMU adds to the high order  $\mu$ Processor address, the contents of the PO register pair or the P1 register pair, respectively, and puts this new address on the bus, including the extended addressing bit A<sub>16</sub>. RAM banking will occur as appropriate to access the new address. Writes to the PO and P1 registers will be stored in a prelatch, until a write to the respective P<sub>XL</sub> register occurs. This prevents a P<sub>XH</sub> register from affecting the translated address until both high and low bytes have been written.

At the same time, the contents of the PO and P1 registers are applied to a digital comparator, and a reverse substitution occurs if the address from the 8502 falls within the page pointed to by the register. This results in not just relocating the zero or one page but swapping the zero or one page with the memory that it replaced. Swapping only occurs if the swapped area is defined as RAM, i.e., System or Function ROM must always be at their assigned addresses and thus should not be back-substituted. Note that upon system reset, the pointers are set to true zero and true one page.

For VIC chip access, one bit in the MMU status register is substituted for extended address line A16, selecting the proper CAS enable to make it possible to steer the VIC to anywhere in the 128K range. Note that AEC is the mechanism that the MMU uses to steer a VIC space address, i.e., when AEC is low a VIC access is assumed. This results in the VIC bank being selected as well for an outside DMA, since this too will pull the AEC line low.

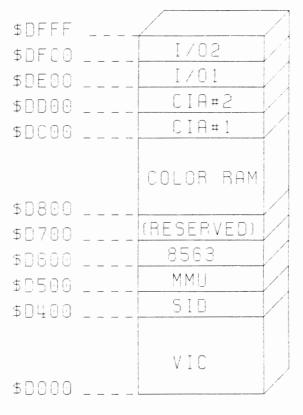

# **MMU and I/O Memory Organization**

The block of memory represented by the **I/O Block** is an expanded view of the memory block entitled **I/O + CHAROM**, as shown in the C128 memory map. When the I/O block exists, access to VIC, SID, and I/O, as well as the addition of the MMU can be accomplished. All I/O functions remain as they were previously on the C64 with the exception that the MMU and the 80 Column chip have been added. With the exception of four registers that are asserted in the zero page in C128 mode, all new MMU registers appear in an unused slot in the I/O Memory block, though they will only appear in C128 mode. Detailed descriptions of the MMU registers can be found in the MMU section on page 20.

I/O Block

# FOLD OUT SCHEMATIC SHEETS 3 AND 4, PAGES 66 AND 67, FOR EASY REFERENCE.

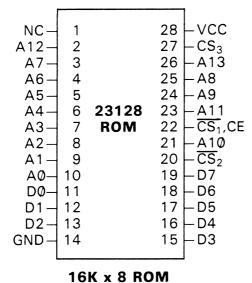

In C64 mode, the operating system resides in 16K of ROM, which includes approximately 8K for Kernal and 8K for Basic. In C128 mode, the operating system resides in 48K of ROM and includes advanced Kernal and Basic features. The Kernal, by definition, is the general operating system of the computer, with fixed entry points into usable subroutines. The entry table for the Kernal is located in memory at addresses \$FF40 - \$FFF9, exluding of course the MMU registers at \$FF00 - \$FF04. There is also a CHARACTER ROM, 8K x 8, which resides on the Shared Bus, shared by the VIC chip and the processor. The C64 OS ROM is wired so as to appear as two chunks of non-contiguous ROM, copying the actual C64 ROM memory map. Provision is included to handle system ROM as either four 16K x 8 ROMs or as two 32K x 8 ROMs. All internal C128 function ROMs will be the 32K x 8 variety.

#### **Rom Banking**

Refer to the **MMU Register Map** on page 20. Note that the Configuration Register (CR) controls the type of ROM or RAM seen in a given address location. Dependent on the contents of the CR, ROM may be enabled and disabled to attain the most useful configuration for the application at hand. ROM is enabled in three memory areas in C128 mode, each consisting of 16K of address space. The lower ROM may be defined as RAM or System ROM, the upper two ROMs may be System ROM, Function ROM, Cartridge ROM, or RAM. In C64 mode the C64 memory mapping rules apply, which are primitive compared to those used in C128 mode. C64 ROM is banked as two 8K sections, BASIC and KERNAL, according to the page zero port and the cartridge in place at the time. No free banking can take place when a cartridge is in place.

In the C128, if an address falls into the range of an enabled ROM, the MMU will communicate the status of ROM to the PLA decoder via the Memory Status lines. Essentially, the MMU looks up in the Configuration Register which ROM or RAM is set. The various combinations possible are shown on the **C128 Memory Map** found on page 11. The banking scheme, the way it is implemented, allows up to 32K of internal, bankable ROM for use such as Function Key Applications programs, and will support 32K of external bankable ROM. Various combinations of ROM are possible, and can be noted by studying the configurations for the Configuration Register.

| A7<br>A6<br>A5<br>A3<br>A3<br>A1<br>A0<br>D0<br>D1<br>D2<br>VSS | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12 | 2364<br>ROM | 24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15<br>14<br>13 |  |

|-----------------------------------------------------------------|-------------------------------------------------------------|-------------|----------------------------------------------------------------------|--|

| 8K | Х | 8 |

|----|---|---|

|----|---|---|

| 1 | 1-8,<br>18,19,<br>21-23 | A0-A12          | Address Bus Inputs |

|---|-------------------------|-----------------|--------------------|

| _ | 12                      | VSS             | Ground.            |

|   | 9-11,<br>13-17          | D0-D7           | Data Outputs.      |

|   | 20                      | CS <sub>1</sub> | Chip Select.       |

| 2 | 24                      | VCC             | 5VDC Input.        |

| PIN           |

|---------------|

| CONFIGURATION |

| 1                     | NC                   | Not Connected.      |

|-----------------------|----------------------|---------------------|

| 2-10,<br>21,<br>23-26 | A0-A13               | Address Bus Inputs. |

| 11-13,<br>15-19       | D0-D7                | Data Outputs.       |

| 14                    | GND                  | Ground.             |

| 20                    | CS <sub>2</sub>      | Chip Select.        |

| 22                    | CS <sub>1</sub> , CE | Output Enable.      |

| 27                    | CS3                  | Program Enable.     |

| 28                    | VCC                  | 5VDC Input.         |

PIN CONFIGURATION

| NC<br>A12<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>D0<br>D1<br>D2<br>GND | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | 23256<br>ROM | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15 |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------|--|

|                                                                        | 32                                                                      | K x 8 RC     | M                                                                                |  |

| 1                     | NC                   | Not Connected.      |

|-----------------------|----------------------|---------------------|

| 2-10,<br>21,<br>23-27 | A0-A14               | Address Bus Inputs. |

| 11-13,<br>15-19       | D0-D7                | Data Outputs.       |

| 14                    | GND                  | Ground.             |

| 20                    | CS <sub>2</sub>      | Chip Select.        |

| 22                    | CS <sub>1</sub> , CE | Output Enable.      |

| 28                    | VCC                  | 5VDC Input.         |

|                       |                      |                     |

# FOLD OUT SCHEMATIC SHEETS 3 AND 4, PAGES 66 AND 67 FOR EASY REFERENCE.

The C128 System contains 128K of processor-addressable 4164 DRAMs in the 64K x 1 configuration, organized into two individual 64K banks. Additionally, the system contains 16K of video display 4416 DRAMs (16K x 4) local to the 8563 CRT Controller, and 8K of STATIC RAM used as VIC COLOR RAM.

RAM banking, described in detail in the MMU section, is controlled by several MMU registers: the Configuration Register, the RAM Configuration Register, and the Page Zero and Page One Pointers. Simply put, the Configuration register controls which 64K bank of RAM is selected, the RAM Configuration Register controls if and how much RAM is kept in common between banks, and the Pointer registers redirect the zero and one pages to any page in memory, overriding the effect of the two configuration registers. In the system, RAM bank select is achieved via gated CAS control.

| 2K x 8 STATIC RAM |   |    |                 |  |

|-------------------|---|----|-----------------|--|

| 1                 |   |    |                 |  |

| A7-               | 1 | 24 | -vcc            |  |

| $A_6-$            | 2 | 23 | - A8            |  |

| A5-               | 3 | 22 | -A9             |  |

| A4-               | 4 | 21 | -WE             |  |

| A3-               | 5 | 20 | — <del>OE</del> |  |

| A2-               | 6 | 19 | -A10            |  |

CS

1/07

-1/06

-1/05

-1/04

-1/03

18

17

16

15

14

13

7

8

9

10

11

12

A1

A0

$1/00^{-1}$

1/01

1/02

Vss

2016

| 1-8,   |           |                                   |

|--------|-----------|-----------------------------------|

| 19, 22 | A0-A10    | Address Bus Inputs.               |

| 23     |           |                                   |

| 9-11,  | 1/00-1/07 | Common Data Input/Output Lines.   |

| 13-17  |           |                                   |

| 12     | VSS       | Ground.                           |

| 18     | CS        | Chip Select Enable, Low Active.   |

| 20     | OE        | Output Enable, Low Active.        |

| 21     | WE        | Write (Input) Enable, Low Active. |

| 24     | Vcc       | 5VDC Input.                       |

#### **RANDOM ACCESS MEMORY (Continued)**

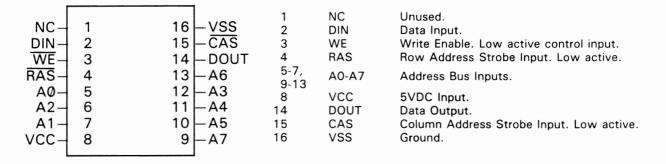

4164 64K x 1 DYNAMIC RAM

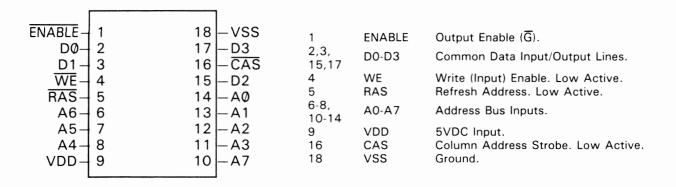

4416 16K x 4 DYNAMIC RAM

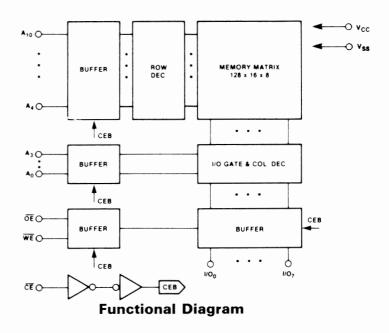

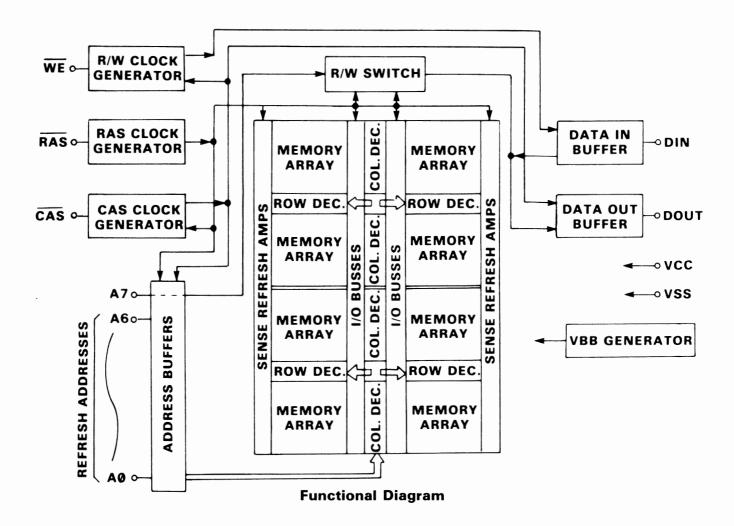

**Functional Diagram**

# FOLD OUT SCHEMATIC SHEET 2, PAGE 65, FOR EASY REFERENCE.

The MMU is designed to allow complex control of the C128 system memory resources. It handles all of the standard **C64 modes of** operation in a fashion as to be completely compatible with the C64. Additionally, it controls the management of particular C128 modes including the Z-80 mode.

Summary of MMU functions:

- Generation of Translated Address Bus, TA<sub>8</sub> TA<sub>15</sub>.

- Generation of control signals for different processor modes C128, C64, Z-80.

- Generation of CAS select lines for RAM banking.

- Generation of ROMBANK (MS<sub>0.</sub> MS<sub>1</sub>) lines for ROM banking.

The MMU is the mechanism by which the various memory modes shown in the C128 Memory Map are chosen. Additionally, the MMU provides for Z-80 mode, which was not shown on that diagram. Following is a description of the MMU register types. Note that in C64 mode the MMU completely disappears from the system's memory map. Note that the data out of the MMU is valid **only** on AEC high. This is necessary to avoid bus contention during a VIC cycle.

**MMU Register Map**

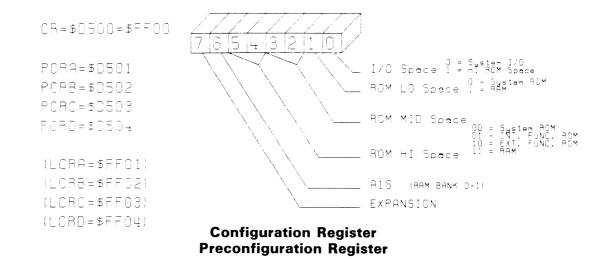

#### **The Configuration Register**

The **Configuration Register**, CR, controls the ROM, RAM, and I/O configuration of the C128 system. It is located at \$D500 in I/O space and at \$FF00 in system space. Some of the bits in this register are at times reflected by hardware lines MS<sub>0</sub> and MS<sub>1</sub> in C128 mode, depending upon how RAM and ROM have been set. These MS lines are used to inform the PLA about the type of memory in a particular address range. In C64 mode, MS<sub>0</sub> and MS<sub>1</sub> are always high, and the selection of RAM and ROM is done by the PLA using standard C64 banking methods. The MS lines are alternately referred to as ROMBANK lines. They will be referred to as MS lines in this section in the interest of simplicity.

In C128 mode, bit 0 controls whether an I/O space, \$D000 – \$DFFF, or a ROM/RAM access occurs. A low will select I/O, a high will enable some kind of ROM/RAM access, the nature of which is controlled by other bits in this register. The value of this bit is stored in a prelatch, until the fall of the clock, in order to prevent its changing in an unstable situation. Note that when not I/O space, the ROM/RAM access is controlled by the defined ROM Hi configuration bits, which are described later. This bit resets to 0. When the I/O bit is low, MMU registers \$D500 to \$D50B will assert themselves. When the bit is high, these registers disappear from the memory map. MMU registers \$FF00 to \$FF04 are always available in C128 mode. The hardware line I/OSE always reflects the polarity of this bit when in C128 mode. In C64 mode the I/OSE line, the hardware line driven by this bit, is completely ignored by the PLA, and the MMU is never asserted, even when C64 I/O is enabled. The C64 method of selecting I/O via HIROM and CHAREN takes over here. The I/O hardware line remains in its set state when in C128 mode, even though it has no effect in this mode.

Bit number 1 controls processor access to ROM low space, \$4000 - \$7FFF, in C128 mode. If the bit is high, the area will appear as RAM, and a RAM access, CAS enable, will be generated to the appropriate RAM bank, which is determined by other bits in this register. If low, system ROM will be located in the space. This bit affects the memory status lines MS0 and MS1 which are decoded by the PLA to generate ROM chip selects. Selecting ROM here will drive both memory status lines low when the processor address falls within the specified low space range. This bit resets low to include the C128 Basic Low ROM. Of course in C64 mode, this bit is ignored.

The next two bits, bits 2 and 3, determine for C128 mode the type of memory that will be located in the mid space, 8000 - BFFF. If they are both low, system ROM will be located here. If bit 2 alone is high, internal function ROM is located here. External function ROM appears for bit 3 being alone high, and RAM appears, along with the proper CAS generation, for both bits set high. These bits also affect the hardware memory access lines. When in the aforementioned mid block address range, MS0 will reflect the status of bit 3, and MS1 will reflect the status of bit 2. These bits both reset low to start out with Basic Hi. C64 mode ignores these bits.

Bits 4 and 5 determine the contents of the Hi block, \$C000 – \$FFFF, for C128 mode, and have no effect on C64 mode. As with the mid space, both bits zero will set up system ROM, bit 4 high will set up internal function ROM, bit 5 high will set up external function ROM, and both bits high will set up RAM. Note that the I/O configuration bit, when set for I/O space, will leave the area from \$D000 to \$DFFF as I/O space, regardless of the values of these bits. If not set for I/O space, \$D000 to \$DFFF will contain the character ROM if the ROM chosen is System ROM. As with the other ROM selection bits, these bits are reflected by the memory status lines when this region of address is accessed. Bit 5 corresponds to MS0 and bit 4 to MS1. Both of these bits reset to low to permit Kernal and Character ROM to power up in this address space. Note that there is always a hole in high ROM during C128 mode for the MMU registers at \$FF00 to \$FF04. This hole is brought about by holding both MS lines high and both CAS enable lines high. These bits are ignored in C64 mode.

Finally, bit 6 controls the RAM bank selection. When low, it will select bank 0 by dropping CAS0. When high, it will select bank 1 by dropping CAS1. Bit 7 is unassigned at the present, left for future expansion. Note that a RAM share status that is non-zero will override the normal CAS enable generation to provide CAS0 for all shared memory. Also, note that when the proper CAS enable is generated, any area of memory, even if that area does not have its ROM bank bits set for RAM, is accessed. It is up to the PLA to block CAS for a read from ROM. This allows RAM bleed through on a write to ROM. For any access to the MMU registers from \$FF00 to \$FF04, in any C128 mode configuration, both CAS enable lines and both MS lines will be high. Note that in C64 mode, the bank used follows the same rules as in C128 mode, though of course banks cannot be changed once in C64 mode.

#### **The Preconfiguration Mechanism**

The Preconfiguration Mechanism is a feature of the MMU that allows the Configuration Register to be loaded with one of several memory configurations, with a minimum of time and memory on the part of the user. The scheme makes use of two sets of registers, the **Preconfiguration Registers** and the **Load Configuration Registers**.

The Preconfiguration Registers (PCRA – PCRD) are used to store several different memory configurations that may be accessed with a single store instruction. The format of each preconfiguration register is the same as for the Configuration Register but, when a value is stored to a preconfiguration register, no immediate effect takes place. They occupy I/O space from D501 to D504. These registers always reset to all zeros.

Load Configuration Registers (LCRA – LCRD) directly correspond with the preconfiguration registers on a one-to-one basis. A write to a Load Configuration Register causes the contents of the corresponding Preconfiguration Register to be transferred to the Configuration Register. A read of any Load Configuration Register returns the value of its corresponding Preconfiguration Register. Load Configuration Registers are located in system space from \$FF01 to \$FF04. Neither the Load Configuration Registers nor the Preconfiguration Registers have any effect in C64 mode. These registers reset to all zeros. Note that these, and the configuration register at \$FF00, will **always** be available, completely independent of the ROM, RAM, or bank configuration defined for Hi ROM space. Any address in this range will cause the MMU to force both memory status lines and both CAS enable lines high.

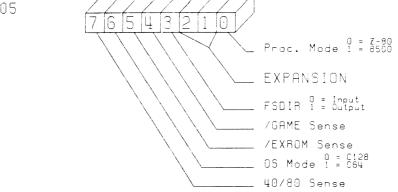

#### **Mode Configuration Register**

#### The Mode Configuration Register

The control of the current system mode is governed by the **Mode Configuration Register**, MCR. It controls which processor, 8502 or Z-80, and which operating system mode, C64 or C128, is currently in operation, and handles other overhead of the different operating modes. This register is located in the I/O space at \$D505.

Several of the bits in this register function as bidirectional ports, including the FSDIR, GAME, EX-ROM, and 40/80 bits. This type of port functions like an output port. If a value is written to the port, its hardware line will reflect that value written, and a read will return that value. The only exception to this is if an external source is pulling down the corresponding port line. When pulled down, a read of the port will return a low. Once the external source has been removed, a read will return the value previously stored. Thus, as an input, the port can be driven low, but not high, by an external source. Under each bit description, both the input and output functions of each port bit will be described in detail.

The first bit, bit 0, controls which processor is enabled. It is reflected by the output line **Z80EN**. When low, it indicates that the processor is the Z-80. This is the reset configuration, and will cause the Z-80 processor to be active and all accesses to memory to follow the Z-80 mapping rules. In Z-80 mode, any address to RAM bank 0 in the range from \$0000 to \$0FFF will be translated to the corresponding address in the range from \$D000 to \$DFFF, where the Z-80 CP/M BIOS physically exists in System ROM. Additionally, the memory status lines MS0 and MS1, will reflect system ROM (both low) for accesses in the range of the BIOS, and the page zero and page one offset pointers will be disabled. RAM can still be banked by the CR A16 bit, which controls CAS0 and CAS1. When in bank one, the BIOS ROM disappears, allowing the RAM from \$0000 to \$FFFF to be used by the system, and enabling the page zero and one offset pointers.

A change to this processor select bit is held in prelatch until a clock transition, in order to prevent processor changing in the midst of an instruction execution. Bringing this bit high will cause the Z-80 to be disabled and the 8502 to take over. Upon system power up, the Z-80 will turn itself off and bring up C128 mode by setting this bit and allowing the 8502 to take over.

Bits 1 and 2 are unused, but are reserved for future expansion as possible port lines. Currently, they will return high if read, and cannot be written to.

Bit 3 is the **FSDIR** control bit. It is used as an output to control the fast serial disk data direction buffer hardware, and as an input to sense a fast disk enable signal. This bit is a bidirectional port bit as explained above, and its hardware line is called **FSDIR**.

Bits 4 and 5 are the GAME and EXROM sense bits, respectively, which are implemented as bidirectional ports as explained above. As inputs, they directly reflect the hardware cartridge control lines GAME and EXROM as used in C64 mode. C128 cartridges do not use EXROM and GAME, so if they are detected in C128 mode, a C64 cartridge is present and C64 mode should be asserted. They have no dedicated C128 function.

The operating system mode is set by bit 6. This bit is cleared to zero upon reset and its presence enables all MMU registers and other C128 features, as well as asserting the C128 control line in hard-ware. Setting this bit removes the MMU from the memory map and sets the system up in C64 mode. Note that the C128 MS3 hardware line reflects a logical inversion of the level of this bit.

Bit 7 is used to detect the status of the screen mode switch, as presented in hardware to the Sense40 column pin. If this bit is high, the 40/80 column switch is open, if low, the switch is closed. The display mode will be set according to a software interpretation of this bit. This bit is a bidirectional port bit, but its output function is undedicated at this time.

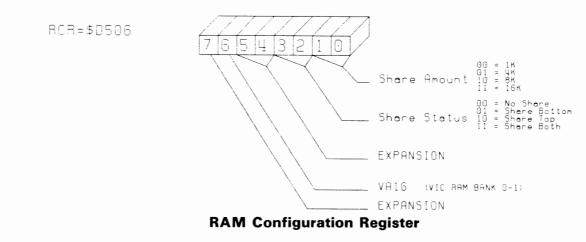

#### The RAM Configuration Register

The **RAM Configuration Register** sets up the RAM segmenting parameters for both the processor and the block pointer for the VIC chip. This register is located in the I/O space at \$D506.

Bits 0 and 1 function together to determine the size of the RAM to be shared between banks, assuming that sharing is enabled. With common RAM, the RAM bank bits of the configuration register are basically overridden, as the selected bank of RAM will be used for the non-common areas, while bank 0 will be used for the specified common areas. ROM and I/O block configuration bits, however, are still important. If the value of the bits together is 0, then 1K of RAM is held common. If the value is 1, then 4K; 2, then 8K; 3, then 16K. These bits have no effect in C64 mode, and the reset value of both bits is defined to be zero.

Bits 2 and 3 function to determine how and if RAM is kept common. If both are low, no sharing takes place. If bit 2 is set, the bottom RAM is shared. If bit 3 is set, the top RAM is shared. Both may be set at the same time for sharing both top and bottom memory. The reset configuration sets both of these bits zero, such that no common memory is present.

The next two bits, numbers 4 and 5, are not used in this MMU. They are available for possible future expansion. They read low, and cannot be written to.

Bit 6 functions as a RAM bank pointer for VIC. It is used to drive CAS0 low when set low or CAS1 low when set high, thus selecting either RAM bank 0 or RAM bank 1 for the VIC, independently from the processor bank. When in 2 MHz mode the 80-column chip takes over, causing the VIC to be disabled. This disabling is affected by the VIC chip itself holding AEC constantly high, and thus is not directly effected by actions of the MMU. Note that since a VIC cycle is detected by AEC low, that any DMA will put the MMU into VIC configuration, as it too brings AEC low. This allows independent bank selection for DMAs in 80 column mode.

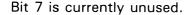

#### **The Page Pointers**

The page pointers are four registers that allow independent relocation of pages zero and one, when running under either processor. These are especially useful when running under the 8502 as they help to remove some of the zero page and stack size limitations normally associated with 6502 family processors.

For zero page relocation, the MMU provides the **Page Zero Pointer High** (PO<sub>H</sub>) and **Page Zero Pointer Low** (PO<sub>L</sub>) registers. Bit 0 of the PO<sub>H</sub> register corresponds to translated addresses TA<sub>16</sub> for any zero page access, \$0000 - \$00FF, controlling the generation of CAS<sub>0</sub> or CAS<sub>1</sub> depending on whether it is low or high. The remaining bits are currently unused, and will always return zero. These bits override the RAM bank bits, the ROM block, and the I/O block bits to determine which physical page appears as zero page for all zero page accesses. A write to the PO<sub>H</sub> register is stored in prelatch until a write to the PO<sub>L</sub> register occurs. Bits 0 to 7 of the PO<sub>L</sub> correspond to Translated Addresses TA<sub>8</sub> to TA<sub>15</sub> for any zero page access, thus relocating the zero page. Any access to the area that has become the relocated zero page will be switched back to the original zero page if that area is mapped as RAM. If mapped as ROM, then the reverse mapping is not done, allowing access to the ROM. A write to this register sets up the zero page transfer, which can occur as soon as the next low clock cycle. Register PO<sub>L</sub> is located in the I/O space at \$D507, while register PO<sub>H</sub> is located at \$D508.

# **COMMON LINE DEFINITIONS**

|            |                                  | · · · · · · · · · · · · · · · · · · · |                                          |

|------------|----------------------------------|---------------------------------------|------------------------------------------|

| A0-A7      | PROCESSOR ADDRESS BUS            | LCR                                   | LOAD CONFIGURATION REGISTER              |

| AEC        | ADDRESS ENABLE CONTROL           | LP                                    | LIGHT PEN INPUT                          |

| ATN        | ATTENTION LINE                   |                                       |                                          |

|            |                                  | MA0-MA11                              | MULTIPLEXED ADDRESS BUS                  |

| BA         | BUS AVAILABLE                    | MMU                                   | MEMORY MANAGEMENT UNIT                   |

|            |                                  | MS 0-4                                | MEMORY STATUS, ALSO INDENTIFIED AS       |

| C128/64    | C128 OR C64 MODE                 |                                       | ROMBANK                                  |

| CAP LK     | CAPITAL LOCK                     | MUX                                   | ADDRESS MULTIPLEX CONTROL                |

| CAS        | DRAM COLUMN ADDRESS STROBE       |                                       | MEMORY MULTIPLEX                         |